### TFT DISPLAY SPECIFICATION

# WINSTAR Display Co.,Ltd. 華凌光電股份有限公司

Distributed by www.texim-europe.com

WEB: <u>https://www.winstar.com.tw</u> E-mail: sales@winstar.com.tw

### **SPECIFICATION**

### CUSTOMER

**MODULE NO.:**

### WF70D5SWAHMNNO#

| SALES BY     | APPROVED BY | CHECKED BY | PREPARED BY |

|--------------|-------------|------------|-------------|

|              |             |            | 葉虹蘭         |

| ISSUED DATE: | 2024/12/16  |            |             |

TFT Display Inspection Specification: <u>https://www.winstar.com.tw/technology/download.html</u> Precaution in use of TFT module: <u>https://www.winstar.com.tw/technology/download/declaration.html</u>

Distributed by www.texim-europe.com

| Wi<br>華 | nstar Display<br>麦光電股份有限 | <b>y Co., LT</b><br>公司 | D  | MODLE NO :       |

|---------|--------------------------|------------------------|----|------------------|

| REC     | ORDS OF REV              | ISION                  |    | DOC. FIRST ISSUE |

| VERSION | DATE                     | REVISED<br>PAGE NO.    | SU | MMARY            |

| 0       | 2024/12/16               |                        | Fi | rst issue        |

## Contents

- 1.Module Classification Information

- 2.Summary

- **3.General Specifications**

- 4. Absolute Maximum Ratings

- **5.**Electrical Characteristics

- 6.MIPI Interface

- 7. Power Sequence

- 8.Optical Characteristics

- 9.Interface

- 10.Reliability

- 11.Contour Drawing

- 12.Initial Code For Reference

# **1.Module Classification Information**

| W | F | 70 | D5 | S   | W | А              | Η | Μ | Ν  | Ν   | 0    | #    |

|---|---|----|----|-----|---|----------------|---|---|----|-----|------|------|

| 1 | 2 | 3  | 4  | (5) | 6 | $\overline{7}$ | 8 | 9 | 10 | (1) | (12) | (13) |

| 1  | Brar                                                                          | nd : WINS             | ΓAR        | DISPLA                 | YC    | ORI   | PORAT    | TION  | J     |       |                                   |      |            |        |             |        | ]     |

|----|-------------------------------------------------------------------------------|-----------------------|------------|------------------------|-------|-------|----------|-------|-------|-------|-----------------------------------|------|------------|--------|-------------|--------|-------|

| 2  | Disp                                                                          | olay Type:            | F→         | ТГТ Туре               | e, J- | →Cı   | istom T  | FT    |       |       |                                   |      |            |        |             |        |       |

| 3  | Disp                                                                          | olay Size : '         | 7.0"       | TFT                    |       |       |          |       |       |       |                                   |      |            |        |             |        |       |

| 4  | Mod                                                                           | lel serials n         | 0.         |                        |       |       |          |       |       |       |                                   |      |            |        |             |        |       |

| 5  | Bacl                                                                          | klight                | F          | →CCFL,                 | Wh    | ite   |          |       |       |       | T-                                | →L   | ED, Whit   | e      |             |        |       |

| 0  | Туре                                                                          | e:                    | S          | →LED, H                | ligh  | Lig   | ght Whi  | te    |       |       | Z→Nichia LED, White               |      |            |        |             |        |       |

|    |                                                                               | ) Polarize            | A          | →Transm                | nissi | ive,  | N.T, IP  | PS T  | FT    |       | Q→Transmissive, Super W.T, 12:00  |      |            |        |             | )      |       |

|    | Тур                                                                           |                       | C          | C→Transm               | nissi | ve,   | N. T, 6  | :00 ; | ;     |       | R                                 | →T   | ransmissi  | ve, S  | uper W.T,   | O-TF   | Τ     |

|    |                                                                               | perature              | F          | →Transm                | issi  | ve, ] | N.T,12:  | :00;  |       |       | V→Transmissive, Super W.T, VA TFT |      |            |        | FT          |        |       |

| 6  |                                                                               | ge/ Gray              | I-         | →Transmi               | issiv | ve, V | W. T, 6: | 00    |       |       | W                                 | ′→]  | Fransmiss  | ive, S | Super W.T,  | IPS '  | TFT   |

|    | -                                                                             | e Inversion           | K          | C→Transfl              | ecti  | ve,   | W.T,12   | :00   |       |       | X                                 | →T   | ransmissi  | ve, V  | V.T, VA TF  | Т      |       |

|    |                                                                               | etion                 | L          | →Transm                | issi  | ve,   | W.T,12   | :00   |       |       | Y                                 | →T   | ransmissi  | ve, V  | V.T, IPS TH | T      |       |

|    | Dire                                                                          |                       | N          | →Transm                | nissi | ive,  | Super V  | W.T,  | , 6:0 | 00    | Z-                                | →T   | ransmissi  | ve, V  | V.T, O-TFT  | 1      |       |

|    | A:                                                                            | TFT LCD               |            |                        |       |       |          |       |       |       | F                                 | : T] | FT+CON     | TRO    | L BOAR      | D      |       |

|    | B:                                                                            | TFT+SCRI              | EW         | HOLES+C                | CON   | VTR   | OL BC    | DAR   | D     |       | G                                 | : T  | FT+ SCR    | EW     | HOLES       |        |       |

| Ø  | C : TFT+ SCREW HOLES +A/D BOARD H : TFT+D/V BOARD                             |                       |            |                        |       |       |          |       |       |       |                                   |      |            |        |             |        |       |

|    | D : TFT+ SCREW HOLES +A/D BOARD+CONTROL BOARD I : TFT+ SCREW HOLES +D/V BOARD |                       |            |                        |       |       |          |       |       |       |                                   |      |            |        |             |        |       |

|    | Е:'                                                                           | TFT+ SCR              | EW         | HOLES +                | PO    | WE    | R BC     | DAR   | D     |       | J                                 | : Tł | T+POW      | ER E   | BD          |        |       |

|    | Reso                                                                          | olution:              |            |                        |       |       |          |       |       |       |                                   |      |            | _      |             |        |       |

|    | Α                                                                             | 12816 <mark>0</mark>  | В          | 320 <mark>2</mark> 34  | С     | 32    | .0240    | D     | 4     | 8023  | 4                                 | E    | 480272     | F      | 640480      |        |       |

| 8  | G                                                                             | 80048 <mark>0</mark>  | Η          | 102 <mark>4</mark> 600 | Ι     | 32    | .0480    | J     | 24    | 4032  | 0                                 | Κ    | 800600     | L      | 240400      |        |       |

|    | Μ                                                                             | 102476 <mark>8</mark> | Ν          | 128128                 | Р     | 12    | 80800    | Q     | 4     | 8080  | 0                                 | R    | 640320     | S      | 480128      |        |       |

|    | Т                                                                             | 800320                | U          | 8001280                | V     | 17    | 6220     | W     | 12    | 8039  | 98                                | Х    | 1024250    | Y      | 1920720     |        |       |

|    | Z                                                                             | 800200                | 2          | 1024324                | 3     | 720   | 01280    | 4     | 192   | 2012  | 00                                | 5    | 1366768    | 6      | 1280320     |        |       |

| 9  | D: E                                                                          | Digital L             | $: \Gamma$ | VDS M:                 | MI    | PI    |          |       |       |       |                                   |      |            |        |             |        |       |

|    | Inter                                                                         | rface:                |            |                        |       |       | 1        |       |       |       |                                   |      |            |        | 1           |        |       |

| 10 | N                                                                             | Without o             | cont       | rol board              |       | А     | 8Bit     |       | В     |       |                                   | 16E  | Bit        | Н      | HDMI        |        |       |

|    | Ι                                                                             | I2C Inter             | face       |                        |       | R     | RS232    | 2     | S     | S     | SPI                               | Inte | erface     | U      | USB         |        |       |

|    | TS:                                                                           | I                     |            |                        |       |       | 1        |       |       |       |                                   |      |            |        |             |        |       |

|    | N                                                                             | Without TS            | 5          |                        |       | Т     | Resist   | ive t | ouc   | ch pa | nel                               |      | C Capac    | itive  | touch pane  | el (G- | ·F-F) |

| 11 | G                                                                             | Capacitive            | tou        | ch panel (             | G-0   | í)    |          |       | (     | C1    | Ca                                | pac  | itive touc | h par  | nel (G-F-F) | +OC    | А     |

|    | C2                                                                            | Capacitive            | tou        | ch panel (             | G-F   | -F)-  | HOCR     |       | (     | Gl    | Ca                                | ipac | itive touc | h par  | nel (G-G)+  | OCA    |       |

|    | G2                                                                            | Capacitive            | tou        | ch panel (             | G-0   | G)+(  | OCR      |       |       | В     | СТ                                | [P+e | GG+USB     |        |             |        |       |

| 12 | Vers                                                                          | ion: X:Ra             | aspb       | erry pi                |       |       |          |       |       |       |                                   |      |            |        |             |        |       |

| 13 | Spee                                                                          | cial Code             |            | #:Fit in v             | vith  | RC    | HS dir   | ectiv | ve r  | egula | atic                              | ons  |            |        |             |        |       |

| L  | 1                                                                             |                       |            |                        |       |       |          |       |       |       |                                   |      |            |        |             |        |       |

## **2.Summary**

The specification WF70D5 is a 7.0" a-Si TFT Liquid Crystal Display ODF cell.

The a-Si TFT-LCD cell will applied to a high transmittance operating in the normally black mode a-Si TFT -LCD product.

WF70D5SWAHMNN0#

第6頁,共36頁

Distributed by www.texim-europe.com

### **3.General Specifications**

| Item             | Dimension                         | Unit |  |  |  |

|------------------|-----------------------------------|------|--|--|--|

| Size             | 7.0                               | inch |  |  |  |

| Dot Matrix       | 1024 x RGB x 600(TFT)             | dots |  |  |  |

| Module dimension | 169.9(W) x 103.4(H) x 5.6(D)      | mm   |  |  |  |

| Active area      | 154.2144 x 85.92                  | mm   |  |  |  |

| Pixel pitch      | 0.1506x 0.1432                    | mm   |  |  |  |

| LCD type         | TFT, Normally Black, Transmissive |      |  |  |  |

| View Angle       | 80/80/80                          |      |  |  |  |

| TFT Driver IC    | JD9165BA or Equivalent            |      |  |  |  |

| TFT Interface    | 4-Lanes MIPI                      |      |  |  |  |

| Backlight Type   | LED,Normally White                |      |  |  |  |

| With /Without TP | Without TP                        |      |  |  |  |

| Surface          | Anti-Glare                        | 90   |  |  |  |

\*Color tone slight changed by temperature and driving voltage.

WF70D5SWAHMNN0#

第7頁,共36頁

### **4.Absolute Maximum Ratings**

| Item                  | Symbol | Min | Тур | Max | Unit |

|-----------------------|--------|-----|-----|-----|------|

| Operating Temperature | TOP    | -30 | _   | +85 | °C   |

| Storage Temperature   | TST    | -40 | _   | +90 | °C   |

Note: Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above

1. Temp.  $\leq 60^{\circ}$ C, 90% RH MAX. Temp. > 60°C, Absolute humidity shall be less than 90% RH at 60°C

WF70D5SWAHMNN0#

第8頁,共36頁

# **5.Electrical Characteristics**

#### 5.1. Operating conditions: Typical Operation Conditions

| ltom                 | Symbol              |      | Values |      | Unit | Demork    |

|----------------------|---------------------|------|--------|------|------|-----------|

| Item                 | Symbol              | Min. | Тур.   | Max. | Onit | Remark    |

| Power voltage        | VDD                 | 1.71 | 1.8    | 1.89 | V    |           |

| Analog Power         | AVDD                | -    | 11     | -    | V    |           |

| TFT Gate ON Voltage  | VGH                 | 19.5 | 20     | 20   | V    | Note1     |

| TFT Gate OFF Voltage | VGL                 | -8.5 | -8     | -7.5 | V    | Note2     |

| TFT Common Voltage   | VCOMIN              | -    | 4.9    | -    | V    | Note3     |

| Power Current        | IDD                 | -    | 14     | 22   | mA   | VDD=1.8V  |

| Analog Power Current | IAVDD               | -    | 18.5   | -    | mA   | AVDD=11V  |

| TFT Gate ON Current  | I <sub>VGH</sub>    | -    | 1.5    | -    | mA   | VGH=20V   |

| TFT Gate OFF Current | Ivgl                | -    | 1.5    | -    | mA   | VGL=-8V   |

| TFT Common Current   | I <sub>VCOMIN</sub> | -    | 1      | -    | uA   | VCOM=4.9V |

Note 1. VGH is TFT Gate operating Voltage.

Note 2. VGL is TFT Gate operating Voltage.

The storage structure of this model is CST (Storage on Common)

Note 3. Vcom must be adjusted to optimize display quality Crosstalk, Contrast Ratio and etc.

WF70D5SWAHMNN0#

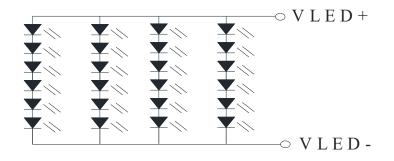

#### 5.2. LED driving conditions

| Parameter     | Symbol | Min.   | Тур. | Max. | Unit | Remark     |

|---------------|--------|--------|------|------|------|------------|

| LED current   | _      | _      | 240  | _    | mA   | -          |

| LED voltage   | VLED+  | 16.2   | 19.2 | 21.0 | V    | Note 1     |

| LED Life Time |        | 50,000 |      |      | Hr   | Note 2,3,4 |

Note 1 : There are 1 Groups LED

B/L CIRCUIT DIAGRAM

Note 2 : Ta = 25 °C

Note 3 : Brightness to be decreased to 50% of the initial value

Note 4 : The single LED lamp case

WF70D5SWAHMNN0#

第10頁,共36頁

# 6.MIPI Interface

#### 6.1. DSI Format

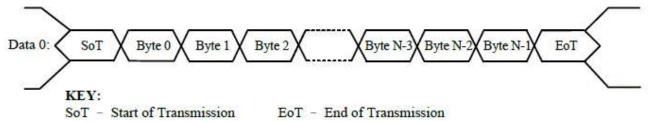

Information is transferred between host processor and peripheral using one or more serial data signals and accompanying serial clock. The action of sending high-speed serial data across the bus is called a HS transmission or burst. Between transmissions, the differential data signal or Lane goes to a low-power state (LPS). Interfaces should be in LPS when they are not actively transmitting or receiving high-speed data. Figure 1 shows the basic structure of a HS transmission. N is the total number of bytes sent in the transmission.

### Figure 1: Basic HS Transmission Structure

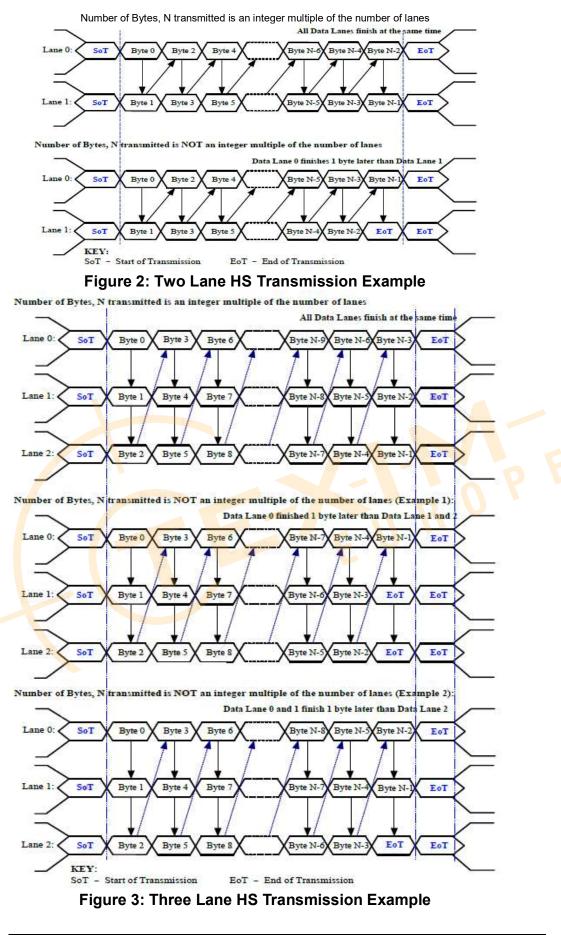

#### Multi Lane Distribution and Merging

DSI is a Lane-scalable interface. Applications requiring more bandwidth than that provided by one Data Lane may expand the data path to two, three, or four Lanes wide and obtain approximately linear increases in peak bus bandwidth.

Multi-Lane implementations shall use a single common clock signal, shared by all Data Lanes. Conceptually, between the PHY and higher functional blocks is a layer that enables multi-Lane operation.

Since a HS transmission is composed of an arbitrary number of bytes that may not be an integer multiple of the number of Lanes, some Lanes may run out of data before others. Therefore, the Lane Management layer, as it buffers up the final set of less-than-N bytes, deaserts its "valid data" signal into all Lanes for which there is no further data.

Although all Lanes start simultaneously with parallel Sots, each Lane operates independently and may complete the HS transmission before the other Lanes, sending an EoT one cycle (byte) earlier.

The N PHYs on the receiving end of the Link collect bytes in parallel and feed them into the Lane Management layer. The Lane Management layer reconstructs the original sequence of bytes in the transmission. Figure 8.4 & 8.5 illustrate a variety of ways a HS transmission can terminate for different number of Lanes and packet lengths.

WF70D5SWAHMNN0#

WF70D5SWAHMNN0#

第12頁,共36頁

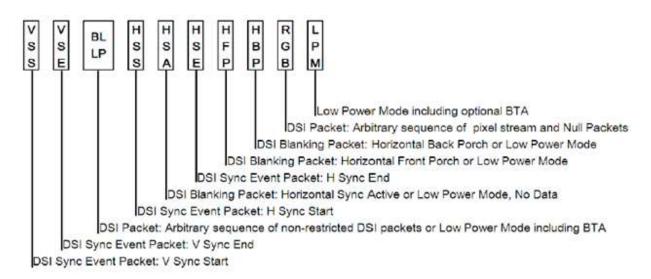

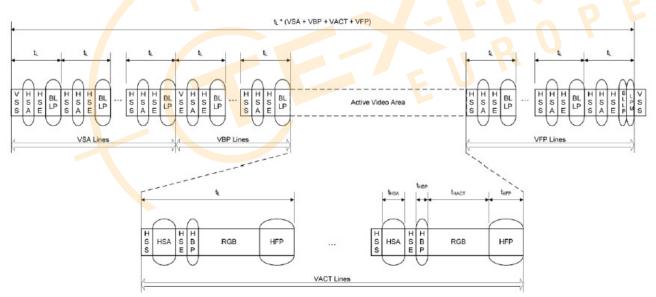

#### 6.2. Video Mode Interface Timing

Video Mode peripherals require pixel data delivered in real time. This section specifies the format and timing of DSI traffic for this type of display module.

#### 1 Transmission Packet Sequences

DSI supports several formats, or packet sequences, for Video Mode data transmission. In the following sections, Burst Mode refers to time-compression of the RGB pixel (active video) portion of the transmission. In addition, these terms are used throughout the following sections:

•Non-Burst Mode with Sync Pulse – enables the peripheral to accurately reconstruct original video timing, including sync pulse widths.

•Non-Burst Mode with Sync Events – similar to above, but accurate reconstruction of sync pulse widths is not required, so a single Sync Event is substituted.

•Burst Mode – RGB pixel packets are time-compressed, leaving more time during a scan line for LP mode (saving power) or for multiplexing other transmissions onto the DSI link. In the following figures the Blanking or Low-Power Interval (BLLP) is defined as a period during which video packets such as pixel-stream and sync event packets are not actively

transmitted to the peripheral.

To enable PHY synchronization the host processor should periodically end HS transmission and drive the Data Lanes to the LP state. This transition should take place at least once per frame; shown as LPM in the figures in this section. The host processor should return to LP state once per scanline during the horizontal blanking time.

During the BLLP the DSI Link may do any of the following:

• Remain in Idle Mode with the host processor in LP-11 state and the peripheral in LP-RX

Transmit one or more non-video packets from the host processor to the peripheral using Escape Mode

• Transmit one or more non-video packets from the host processor to the peripheral using HS Mode

• If the previous processor-to-peripheral transmission ended with BTA, transmit one or more packets from the peripheral to the host processor using Escape Mode

• Transmit one or more packets from the host processor to a different peripheral using a different Virtual Channel ID

The sequence of packets within the BLLP or RGB portion of a HS transmission is arbitrary. The host processor may compose any sequence of packets, including iterations, within the limits of the packet format definitions. For all timing cases, the first line of a frame shall start with VSS; all other lines shall start with VSE or HSS. Note that the position of synchronization packets, such as VSS and HSS, in time is of utmost importance since this has a direct impact on the visual performance of the display panel.

Normally, RGB pixel data is sent with one full scan line of pixels in a single packet.

Transmission packet components used in the figures in this section are defined in Figure 4 unless otherwise specified.

WF70D5SWAHMNN0#

#### Figure 4: Video Mode Interface Timing Legend

If a peripheral timing specification for HBP or HFP minimum period is zero, the corresponding Blanking Packet may be omitted. If the HBP or HFP maximum period is zero, the corresponding blanking packet shall be omitted.

#### 2. Non-Burst sync pulse mode

With this format, the goal is to accurately convey DPI-type timing over the DSI serial Link. This includes matching DPI pixel-transmission rates, and width of timing events like sync pulses. Accordingly, synchronization periods are defined using packets transmitting both start and end of sync pulses. An example of this mode is shown in Figure 5

#### Figure 5: Video Mode Interface Timing: Non-Burst Transmission with Sync Start and End

Normally, periods shown as HAS (Horizontal Sync Active), HBP (Horizontal Back Porch) and HFP (Horizontal Front Porch) are filled by Blanking Packets, with lengths (including packet overhead) calculated to match the period specified by the peripheral's data sheet. Alternatively, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power. During HAS, HBP and HFP periods, the bus should stay in the LP-11 state.

WF70D5SWAHMNN0#

第14頁,共36頁

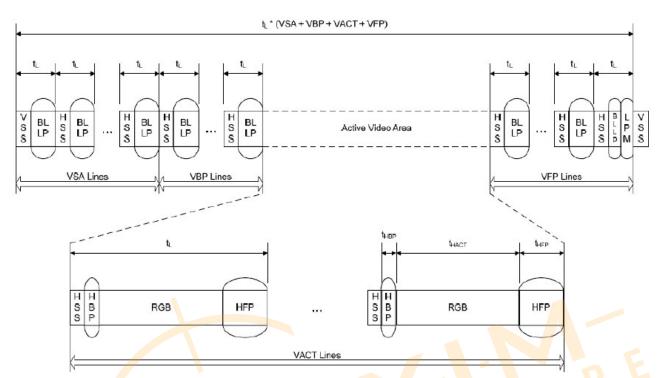

#### 3. Non-Burst sync event mode

This mode is a simplification of the "Non-Burst Mode with Sync Pulses" format. Only the start of each synchronization pulse is transmitted. The peripheral may regenerate sync pulses as needed from each Sync Event packet received. An example of this mode is shown in Figure 6.

Figure 6: Video Mode Interface Timing: Non-Burst Transmission with Sync Events As with the previous Non-Burst Mode, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power.

WF70D5SWAHMNN0#

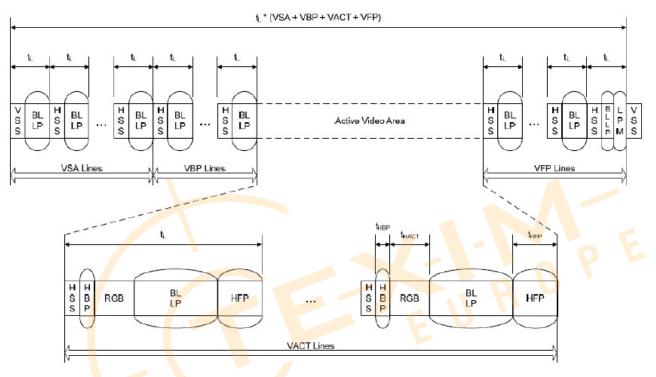

#### 4. Burst mode

In this mode, blocks of pixel data can be transferred in a shorter time using a timecompressed burst format. This is a good strategy to reduce overall DSI power consumption, as well as enabling larger blocks of time for other data transmissions over the Link in either direction.

Following HS pixel data transmission, the bus may stay in HS Mode for sending blanking packets or go to Low Power Mode, during which it may remain idle, i.e. the host processor remains in LP-11 state, or LP transmission may take place in either direction. If the peripheral takes control of the bus for sending data to the host processor, its transmission time shall be limited to ensure data underflow does not occur from its interval buffer memory to the display device. An example of this mode is shown in Figure 7

#### Figure 7: Video Mode Interface Timing: Burst Transmission

Similar to the Non-Burst Mode scenario, if there is sufficient time to transition from HS to LP mode and back again, a timed interval in LP mode may substitute for a Blanking Packet, thus saving power.

#### 6.3. DC characteristic

| Parameter                | Symbol | Rating |     |        | Unit | Condition |  |

|--------------------------|--------|--------|-----|--------|------|-----------|--|

| Farameter                | Symbol | Min    | Тур | Мах    | Unit | Condition |  |

| Low level input voltage  | VIL    | 0      | -   | 0.2VDD | V    |           |  |

| High level input voltage | VIH    | 0.8VDD | -   | VDD    | V    | Note 1    |  |

Note 1:RESET, UPDN,SHLR

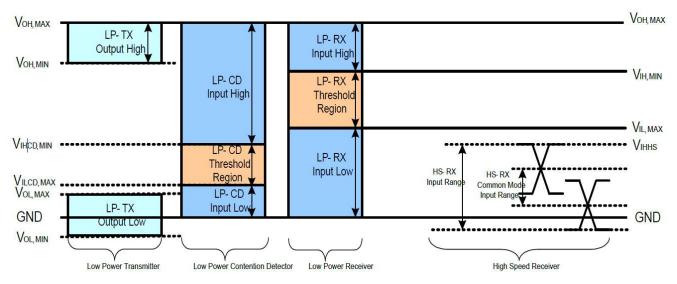

#### M6.4. IPI DC characteristic

| Parameter                                                                            | Symbol               | Min.      | Тур. | Max.        | Unit |

|--------------------------------------------------------------------------------------|----------------------|-----------|------|-------------|------|

| MIPI Characteristics for High Speed Receiver                                         |                      |           |      |             | •    |

| Single-ended input low voltage                                                       | V <sub>ILHS</sub>    | -40       | -    | -           | mV   |

| Single-ended input high voltage                                                      | V <sub>IHHS</sub>    | -         | -    | 460         | mV   |

| Common-mode voltage                                                                  | VCMRXDC              | 70        | -    | 330         | mV   |

| Differential input impedance                                                         | ZID                  | 80        | 100  | 120         | ohm  |

| HS transmit differential voltage(V <sub>OD</sub> =V <sub>DP</sub> -V <sub>DN</sub> ) | VOD                  | 100       | 200  | 250         | mV   |

| MIPI Characte                                                                        | ristics for Low Po   | ower Mode |      |             |      |

| Pad signal voltage range                                                             | VI                   | -50       | - /  | 1350        | mV   |

| Ground shift                                                                         | V <sub>GNDSH</sub>   | -50       | -    | 50          | mV   |

| Logic 0 input thre <mark>sh</mark> old                                               | VIL                  | 0         | -    | <u>55</u> 0 | mV   |

| Logic 1 input th <mark>re</mark> shold                                               | VIH                  | 1000      |      | 1350        | mV   |

| Input hysteres <mark>i</mark> s                                                      | V <sub>HYST</sub>    | 25        |      | -           | mV   |

| Output low le <mark>v</mark> el                                                      | Vol                  | -50       | -    | 50          | mV   |

| Output high l <mark>e</mark> vel                                                     | V <sub>он</sub>      | 1.1       | 1.2  | 1.3         | V    |

| Output imped <mark>a</mark> nce of Low Power Tr <mark>an</mark> smitter              | ZOLP                 | 110       |      |             | ohm  |

| Logic 0 conte <mark>nti</mark> on threshold                                          | VILCD,MAX            | -         | -    | 200         | mV   |

| Logic 1 contention threshold                                                         | VIHCD,MIN            | 450       | -    | -           | mV   |

| MIPI Digital Operating Current                                                       | I <sub>VDDMIPI</sub> | -         | 15   | 20          | mA   |

| MIPI Digital Stand-by Current                                                        | I <sub>STMIPI</sub>  | -         | -    | 250         | uA   |

Note: MIPI Digital Operating and Stand-by Current is at RT 25°C condition.

WF70D5SWAHMNN0#

Figure 8: MIPI signaling and contention voltage levels

WF70D5SWAHMNN0#

第18頁,共36頁

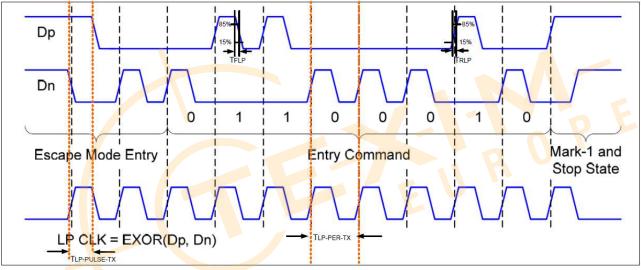

#### 6.5. MIPI AC characteristic 1.MIPI Low Power Transmitter AC Specification

| Parameter                            |                                                                                     | Symbol                             | Min | Тур | Max | Units | Notes |

|--------------------------------------|-------------------------------------------------------------------------------------|------------------------------------|-----|-----|-----|-------|-------|

| 15%~85% rising                       | time and falling time                                                               | T <sub>RLP</sub> /T <sub>FLP</sub> | -   | -   | 25  | ns    | -     |

| 30%~85% rising time and falling time |                                                                                     | T <sub>REOT</sub>                  | -   | -   | 35  | ns    | -     |

|                                      | First LP EXOR clock<br>pulse after STOP state or<br>Last pulse before stop<br>state | T <sub>LP-PULSE-TX</sub>           | 100 | -   | -   | ns    | -     |

|                                      | All other pulses                                                                    |                                    | 100 | -   | -   | ns    | -     |

| Period of the LP I                   | EXOR clock(LP Speed)                                                                | T <sub>LP-PER-TX</sub>             | 200 | -   | -   | ns    | -     |

| Slew Rate @CLC                       | DAD =0pF                                                                            |                                    | 20  | -   | 500 | mV/ns | -     |

| Slew Rate @CLC                       | )AD =5pF                                                                            | 27/124                             | 20  | -   | 200 | mV/ns | -     |

| Slew Rate @CLOAD =20pF               |                                                                                     | δ V/δ t <sub>sr</sub>              | 20  | -   | 150 | mV/ns | -     |

| Slew Rate @CLOAD =70pF               |                                                                                     |                                    | 20  | -   | 100 | mV/ns | -     |

| Load Capacitance                     |                                                                                     | T <sub>RLP</sub>                   | -   | -   | 70  | pF    | -     |

Figure 9: MIPI LP AC timing

WF70D5SWAHMNN0#

第19頁,共36頁

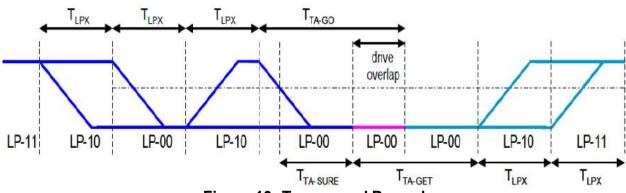

### 2.MIPI Low Power Turnaround Procedure

| Parameter                                    | Symbol               | Min              | Тур               | Max               | Units |  |  |  |

|----------------------------------------------|----------------------|------------------|-------------------|-------------------|-------|--|--|--|

| Length of any Low-Power state period         | T <sub>LPX</sub>     | 100              | -                 | -                 | ns    |  |  |  |

| Time-out before new TX side start driving    | T <sub>TA-Sure</sub> | T <sub>LPX</sub> | -                 | 2T <sub>LPX</sub> | ns    |  |  |  |

| Time to drive LP-00 by new TX                | T <sub>TA-GET</sub>  | -                | 5T <sub>LPX</sub> | -                 | ns    |  |  |  |

| Time to drive LP-00 after Turnaround Request | T <sub>TA-GO</sub>   | -                | 4T <sub>LPX</sub> | -                 | ns    |  |  |  |

Figure 10: Turnaround Procedure

WF70D5SWAHMNN0#

第20頁,共36頁

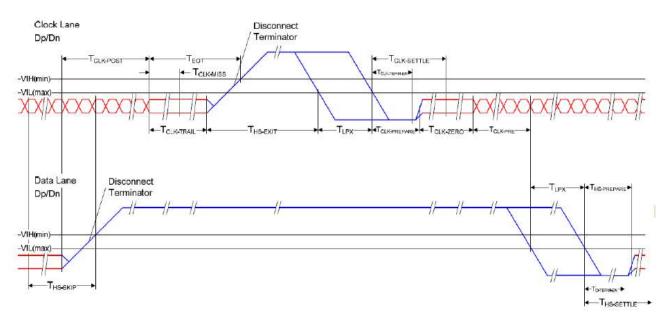

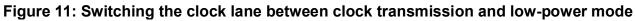

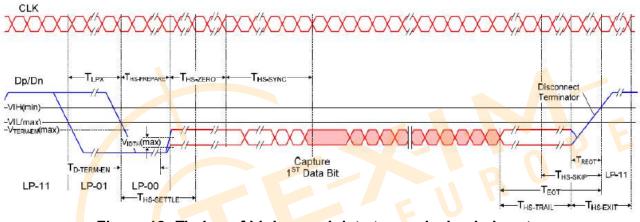

#### **3.MIPI High Speed AC characteristics** DP: D0P/ D1P/D2P/D3P DN: D0N/ D1N /D2N/D3P

| Parameter                 | Descript                                                                                                                                                                                                                      | Spec.                            |                    |     |                   | Unit |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--------------------|-----|-------------------|------|

| Falametei                 | Descript                                                                                                                                                                                                                      | Min.                             | Ту                 | p.  | Max.              | Unit |

| T <sub>REOT</sub>         | 30%-85% rise time and fall time                                                                                                                                                                                               | -                                | -                  |     | 35                | ns   |

| T <sub>CLK-MISS</sub>     | Timeout for receiver to detect absence of Clock<br>transitions and disable the Clock Lane HS-RX.                                                                                                                              |                                  |                    |     | 60                | ns   |

| T <sub>CLK-POST</sub> *1  | Time that the transmitter continues to send HS clock<br>after the last associated Data Lane has<br>transitioned to LP Mode. Interval is defined as the<br>period from the end of THS-TRAIL to the beginning<br>of TCLK-TRAIL. |                                  |                    |     |                   | ns   |

| T <sub>CLK-PRE</sub>      | Time that the HS clock shall be driven by the transmitter prior to any associated Data Lane beginning the transition from LP to HS mode.                                                                                      | 8                                | -                  |     |                   | UI   |

| T <sub>CLK-SETTLE</sub>   | Time interval during which the HS receiver shall ignore any Clock Lane HS transitions, starting from the beginning of TCLK-PRE.                                                                                               | 95                               | -                  |     | 300               | ns   |

| T <sub>clk-term-en</sub>  | Time for the Clock Lane receiver to enable the HS<br>line termination, starting from the time point when<br>Dn crosses VIL,MAX.                                                                                               | Time for Dn to<br>reach VTERM-EN |                    |     | 38                | ns   |

| T <sub>HS-SETTLE</sub>    | Time interval during which the HS receiver shall ignore any Data Lane HS transitions, starting from the beginning of THSPREPARE.                                                                                              | 85 n <mark>s +</mark> 6*UI       |                    |     | 145 ns +<br>10*UI | ns   |

| Т <sub>ЕОТ</sub>          | Time from start of THS-TRAIL or TCLK-TRAIL period to start of LP-11 state                                                                                                                                                     | - P                              |                    | 1   | 05ns+n*1<br>2*UI  | -    |

| T <sub>HS-EXIT</sub> (1)  | time to driv <mark>e</mark> LP-11 after HS burst                                                                                                                                                                              | 100                              | -                  |     | -                 | ns   |

| T <sub>HS-PREPARE</sub>   | Time to drive LP-00 to prepare for HS transmission                                                                                                                                                                            | 40ns + 4*U                       | ı   -              | 8   | 5ns+6*UI          | ns   |

| Ths-prepare<br>+ Ths-zero | THS-PREPARE + Time to drive HS-0 before the<br>Sync sequence                                                                                                                                                                  | 145ns + 10*UI                    |                    |     | -                 | ns   |

| T <sub>HS-SKIP</sub>      | Time-out at RX to ignore transition period of EoT                                                                                                                                                                             | 40                               | -                  | 5   | 5ns+4*UI          | ns   |

| T <sub>HS-TRAIL</sub>     | Time to drive flipped differential state after last payload data bit of a HS transmission burst                                                                                                                               | 60 + 4*UI -                      |                    |     | -                 | ns   |

| T <sub>LPX</sub>          | Length of any Low-Power state period                                                                                                                                                                                          | 100                              |                    |     | -                 | ns   |

| Ratio T <sub>LPX</sub>    | Ratio of TLPX(MASTER)/TLPS(SLAVE) between<br>Master and Slave side                                                                                                                                                            | 2/3 - 3/2                        |                    | 3/2 | -                 |      |

| T <sub>TA-GET</sub>       | Time to drive LP-00 by new TX                                                                                                                                                                                                 |                                  | $5^{*}T_{LPX}$     |     |                   | ns   |

| T <sub>TA-GO</sub>        | Time to drive LP-00 after Turnaround Request                                                                                                                                                                                  | ļ                                | 4*T <sub>LPX</sub> |     |                   | ns   |

| T <sub>TA-SURE</sub>      | Time-out before new TX side starts driving                                                                                                                                                                                    | T <sub>LPX</sub>                 | -                  | 2*  | T <sub>LPX</sub>  | ns   |

Note: (1) For T<sub>CLK-POST</sub> example:

$T_{CLK-POST}$  min value =164UI when MIPI max frequency per lane = 0.5Gbps.

T<sub>CLK-POST</sub> min value =112UI when MIPI max frequency per lane = 1Gbps (2) For TEOT:

When n = 1 for Forward-direction HS mode and n=4 for Reverse-direction HS mode

WF70D5SWAHMNN0#

第21頁,共36頁

Figure 12: Timing of high-speed data transmission in bursts

WF70D5SWAHMNN0#

第22頁,共36頁

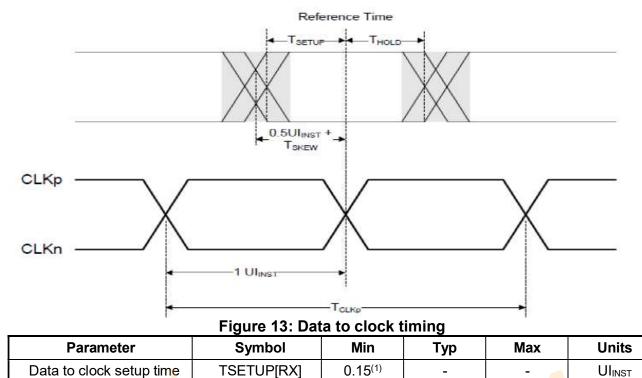

#### 4.MIPI data-clock timing specification

|                                                                    | Data to clock hold time | THOLD[RX]            | 0.15 <sup>(1)</sup> | -            |  | - |  |

|--------------------------------------------------------------------|-------------------------|----------------------|---------------------|--------------|--|---|--|

| Note: (1) Total setup and hold window for receiver of 0.3* UIINST. |                         |                      |                     |              |  |   |  |

|                                                                    | Т                       | able 1: Data to Cloo | ck Timing Sp        | ecifications |  |   |  |

WF70D5SWAHMNN0#

第23頁,共36頁

UIINST

### 6.6. MIPI timing characteristic

| MIDI Innut Timin -                             | Sumhel | 1    | 024RGBx60 | 0     | Unit |  |

|------------------------------------------------|--------|------|-----------|-------|------|--|

| MIPI Input Timing                              | Symbol | Min  | Тур       | Мах   | Unit |  |

| MIPI 24-bit RGB@ 2 lane<br>Operating Frequency | -      | 400  | 616       | 750   | Mbps |  |

| MIPI 24-bit RGB@ 4 lane<br>Operating Frequency | -      | 200  | 308       | 500   | Mbps |  |

| Frame Rate@ 2 lane                             | -      | 48   | 60        | -     | Hz   |  |

| Frame Rate@ 4 lane                             | -      | 48   | 60        | -     | Hz   |  |

| Horizontal Total                               | tht    | 1114 | 1344      | 1400  | DCLK |  |

| Hsync Pulse width                              | ths    | 1    | 24        | HBP-1 | DCLK |  |

| Horizontal Back Porch                          | thb    | 60   | 160       | 160   | DCLK |  |

| Horizontal Valid Data                          | thd    |      | 1024      |       | DCLK |  |

| Horizontal Front Porch                         | thfp   | 30   | 160       | 216   | DCLK |  |

| Vertical Total                                 | t∨t    | 620  | 635       | 800   | THT  |  |

| Vsync Pulse Width                              | tvs    | 1    | 2         | VBP-1 | THT  |  |

| Vertical Back Porch                            | tvb    | 8    | 23        | 100   | ТНТ  |  |

| Vertical Valid Data                            | tvd    |      | 600       |       | THT  |  |

| Vertical Front Porch                           | tvfp   | 12   | 12        | 100   | ТНТ  |  |

WF70D5SWAHMNN0#

第24頁,共36頁

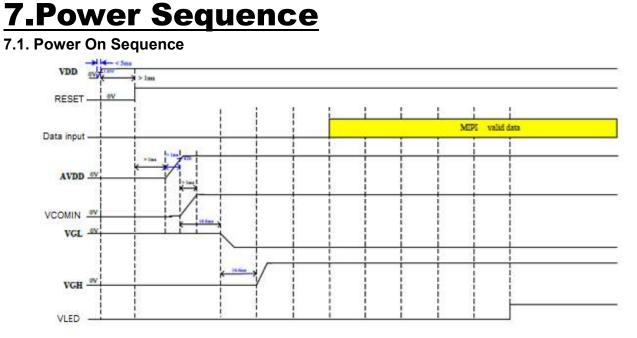

Figure 14: Power On timing chart

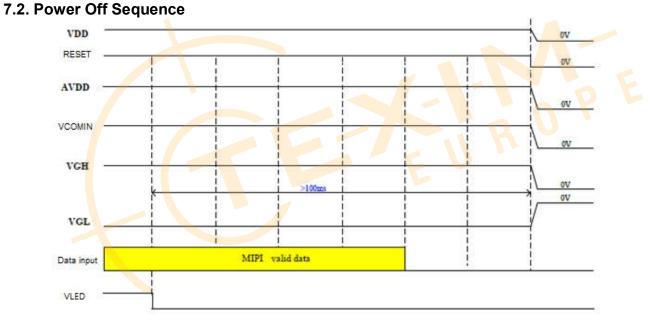

Figure 15: Power Off timing chart

## **8.Optical Characteristics**

#### TFT LCD characteristic

| Item           |                 | Symbol | Condition.                    | Min   | Тур.  | Max.  | Unit              | Remark               |

|----------------|-----------------|--------|-------------------------------|-------|-------|-------|-------------------|----------------------|

| Response ti    | me              | Tr+ Tf | θ=0°、Φ=0°                     | -     | 30    | 35    | .ms               | Note 3               |

| Contrast ratio |                 | CR     | At optimized<br>viewing angle | 700   | 1000  | -     | -                 | Note 4               |

| Color          | White           | Wx     | θ=0°、Φ=0                      | 0.264 | 0.314 | 0.364 | -                 | Noto 2.6.7           |

| Chromaticity   | vvnite          | Wy     |                               | 0.272 | 0.322 | 0.372 | -                 | Note 2,6,7           |

|                | Hor<br>ngle Ver | ΘR     | CR≧10                         | 70    | 80    | -     | Deg.              |                      |

|                |                 | ΘL     |                               | 70    | 80    | -     |                   | Note 1               |

| Viewing angle  |                 | ФТ     |                               | 70    | 80    | -     |                   | Note 1               |

|                |                 | ФВ     |                               | 70    | 80    | -     |                   |                      |

| Brightness     | 6               | -      | -                             | 1200  | 1300  | -     | cd/m <sup>2</sup> | Center of<br>display |

| Uniformity     | /               | (U)    | -                             | 75    | -     | -     | %                 | Note 5               |

Ta=25±2°C,

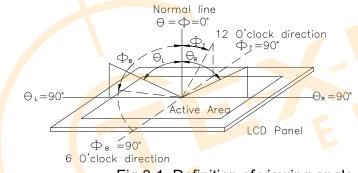

Note 1: Definition of viewing angle range

Fig.8.1. Definition of viewing angle

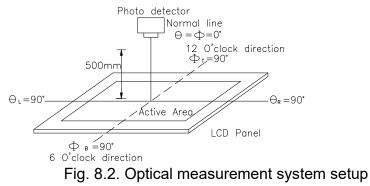

Note 2: Test equipment setup:

After stabilizing and leaving the panel alone at a driven temperature for 10 minutes, the measurement should be executed. Measurement should be executed in a stable, windless, and dark room. Optical specifications are measured by Topcon BM-7orBM-5 luminance meter 1.0° field of view at a distance of 50cm and normal direction.

WF70D5SWAHMNN0#

第26頁,共36頁

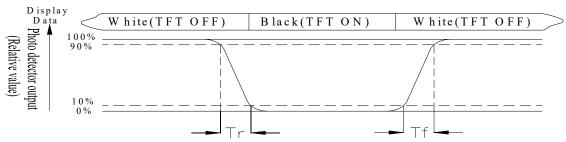

Note 3: Definition of Response time:

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time, Tr, is the time between photo detector output intensity changed from 90% to 10%. And fall time, Tf, is the time between photo detector output intensity changed from 10% to 90%

Note 4: Definition of contrast ratio:

The contrast ratio is defined as the following expression.

Contrast ratio (CR) = Luminance measured when LCD on the "White" state Luminance measured when LCD on the "Black" state

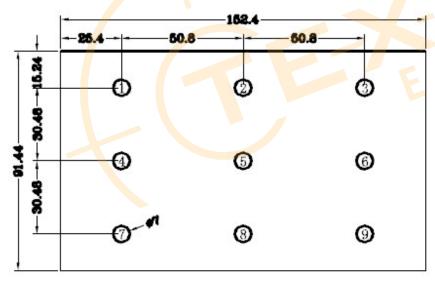

Note 5: Definition of Luminance Uniformity

Active area is divided into 9 measuring areas (reference the picture in below). Every measuring point is placed at the center of each measuring area.

Luminance Uniformity (U) = Lmin/Lmax x100%

L = Active area length

W = Active area width

Fig8.3. Definition of uniformity

Note 6: Definition of color chromaticity (CIE 1931) Color coordinates measured at the center point of LCD

Note 7: Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

WF70D5SWAHMNN0#

第27頁,共36頁

# 9.Interface

### 9.1. LCM PIN Definition

| Pin No. | Symbol | Function                                                                                                                  | Remark |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------|--------|

| 1       | VLED+  | LED Anode                                                                                                                 |        |

| 2       | VLED+  | LED Anode                                                                                                                 |        |

| 3       | VGH    | Positive power for TFT                                                                                                    |        |

| 4       | VGL    | Negative power for TFT                                                                                                    |        |

| 5       | UPDN   | Horizontal inversion                                                                                                      |        |

| 6       | SHLR   | Vertical inversion                                                                                                        |        |

| 7       | VLED-  | LED Cathode                                                                                                               |        |

| 8       | VLED-  | LED Cathode                                                                                                               |        |

| 9       | AVDD   | Power for Analog Circuit                                                                                                  |        |

| 10      | GND    | Ground                                                                                                                    |        |

| 11      | D3P    | MIPI data input.                                                                                                          |        |

| 12      | D3N    | MIPI data input.                                                                                                          |        |

| 13      | GND    | Ground                                                                                                                    | ) E    |

| 14      | D2P    | MIPI data input.                                                                                                          |        |

| 15      | D2N    | MIPI data input.                                                                                                          |        |

| 16      | GND    | Ground                                                                                                                    |        |

| 17      | CLKP   | MIPI clock input                                                                                                          |        |

| 18 🧹    | CLKN   | MIPI clock input                                                                                                          |        |

| 19      | GND    | Ground                                                                                                                    |        |

| 20      | D1P    | MIPI data input.                                                                                                          |        |

| 21      | D1N    | MIPI data input.                                                                                                          |        |

| 22      | GND    | Ground                                                                                                                    |        |

| 23      | D0P    | MIPI data input.                                                                                                          |        |

| 24      | D0N    | MIPI data input.                                                                                                          |        |

| 25      | GND    | Ground                                                                                                                    |        |

| 26      | NC     | No connection                                                                                                             |        |

| 27      | RESET  | Global reset pin. Active Low to enter Reset State. Normally pull high. Connecting with an RC reset circuit for stability. |        |

WF70D5SWAHMNN0#

第28頁,共36頁

| 28 | VDD(1.8V) | Digital circuit |  |

|----|-----------|-----------------|--|

| 29 | VDD(1.8V) | Digital circuit |  |

| 30 | VCOMIN    | Common voltage  |  |

#### Note

When SHLR ="1",set right to left scan direction. When SHLR ="0",set left to right scan direction. When UPDN ="0",set top to bottom scan direction. When UPDN ="1",set bottom to top scan direction

WF70D5SWAHMNN0#

第29頁,共36頁

Distributed by www.texim-europe.com

# 10.Reliability

Content of Reliability Test (Super Wide temperature, -30°C~85°C)

| Environmental Test                      |                                                                                                                            |                                                                                                                                                          |      |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Test Item                               | Content of Test                                                                                                            | Test Condition                                                                                                                                           | Note |

| High Temperature<br>storage             | Endurance test applying the high storage temperature for a long time.                                                      | 90°C<br>200hrs                                                                                                                                           | 2    |

| Low Temperature<br>storage              | Endurance test applying the low storage temperature for a long time.                                                       | -40°C<br>200hrs                                                                                                                                          | 1,2  |

| High Temperature<br>Operation           | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.     | 85°C<br>200hrs                                                                                                                                           |      |

| Low Temperature<br>Operation            | Endurance test applying the electric stress under low temperature for a long time.                                         | -30°C<br>200hrs                                                                                                                                          | 1    |

| High Temperature/<br>Humidity Operation | The module should be allowed to stand at 60°C,90%RH max                                                                    | 60°C,90%RH<br>96hrs                                                                                                                                      | 1,2  |

| Thermal shock<br>resistance             | The sample should be allowed stand the following 10 cycles of operation<br>-30°C 25°C 85°C<br>-30min 5min 30min<br>1 cycle | -30°C/85°C<br>10 cycles                                                                                                                                  |      |

| Vibration test                          | Endurance test applying the vibration during transportation and using.                                                     | Total fixed<br>amplitude : 1.5mm<br>Vibration<br>Frequency :<br>10~55Hz<br>One cycle 60<br>seconds to 3<br>directions of<br>X,Y,Z for Each 15<br>minutes | 3    |

| Static electricity test                 | Endurance test applying the electric stress to the terminal.                                                               | VS=TBD(Contact),<br>TBD(air),<br>RS=330Ω<br>CS=150pF<br>10 times                                                                                         |      |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal Temperature and humidity after remove from the test chamber.

Note3: The packing have to including into the vibration testing.

WF70D5SWAHMNN0#

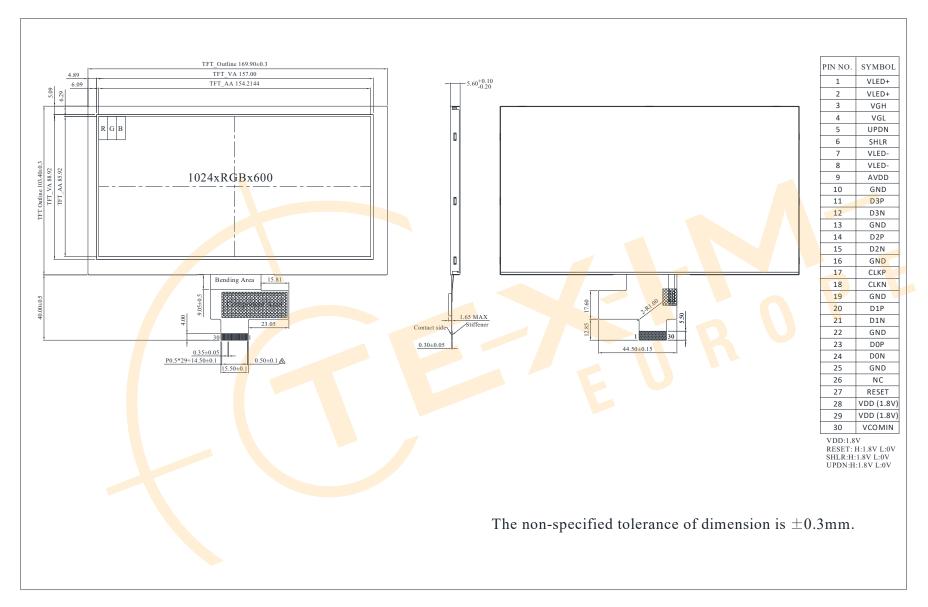

# **11.Contour Drawing**

## **12.Initial Code For Reference**

void JD9165A\_tft\_config(void)

{

// resolution

TFT\_CFG.Horizontal = 1024;

TFT\_CFG.Vertical = 600;

TFT\_CFG.HFP = 160; TFT\_CFG.HBP = 136; TFT\_CFG.HPW = 24;

TFT\_CFG.VFP = 12; TFT\_CFG.VBP = 21; TFT\_CFG.VPW = 2; TFT\_CFG.PCLK = 51200; TFT\_CFG.REFRESH\_RATE = 60;

// bmp address TFT\_CFG.BMP\_ADDR = 0x000000;

// display chip TFT\_CFG.SSD1963 = ssd1963\_null; TFT\_CFG.RA8876 = ra8876\_initial; TFT\_CFG.RA8877 = ra8877\_null; TFT\_CFG.SSD2828 = ssd2828\_initial;

// RA8876 OSC

TFT\_CFG.OSC\_FREQ = 10;

TFT\_CFG.SCAN\_FREQ = 51;

TFT\_CFG.CORE\_FREQ = TFT\_CFG.SCAN\_FREQ \* 2;

TFT\_CFG.DRAM\_FREQ = TFT\_CFG.CORE\_FREQ;

// RA8876 parameter TFT\_CFG.RA8876\_TFT\_Panel\_Output = TFT\_24bits; TFT\_CFG.HostDataBus\_Width = Host\_16bits\_DataBus; TFT\_CFG.Memory\_Write\_Direction = 0; TFT\_CFG.MainImage\_ColorDepth = COLOR\_DEPTH\_16BPP; TFT\_CFG.synchronous\_signals = Sync\_Mode; TFT\_CFG.PCLK\_Inversion = RISING; TFT\_CFG.AW\_COLOR\_DEPTH = COLOR\_DEPTH\_16BPP;

// SSD2828 parameter TFT\_CFG.HSYNC\_POLARITY = LOW\_ACTIVE; TFT\_CFG.VSYNC\_POLARITY = LOW\_ACTIVE; TFT\_CFG.LAUNCH\_TYPE = RISING; TFT\_CFG.ORDER = RGB; // mipi setting TFT\_CFG.LANE = 4; TFT\_CFG.DEPTH = bpp24;

WF70D5SWAHMNN0#

第32頁,共36頁

TFT CFG.LANE SPEED = (uint64 t)TFT CFG.PCLK \* calc bpp(TFT CFG.DEPTH) / TFT CFG.LANE / 1000;

}

{

// Touch IC TFT CFG.TP = ILI2130; TFT CFG.FINGER = 5; TFT CFG.CTP RES.XMIN = 0; TFT CFG.CTP RES.XMAX = 16384; TFT CFG.CTP RES.YMIN = 0; TFT CFG.CTP RES.YMAX = 16384; TFT\_CFG.POINT\_SIZE = 6; void JD9165A init config(void) mipi dsi dcs write 1P(0x30, 0x00); mipi dsi dcs write seq(0xF7, 0x49, 0x61, 0x02, 0x00); mipi dsi dcs write 1P(0x30, 0x01); mipi dsi dcs write 1P(0x04, 0x00); // R04h[2]SHLR · R04h[3]UPDN setting by H/W pin // mipi dsi dcs write 1P(0x05, 0x01); // BIST EN setting by register // mipi dsi dcs write 1P(0x06, 0x41); // BIST mode r shlr=1 mipi dsi dcs write 1P(0x06, 0x01); // r shlr=1 mipi dsi dcs write 1P(0x0B, 0x10); mipi dsi dcs write 1P(0x1F, 0x05); mipi dsi dcs write 1P(0x23, 0x3C); mipi dsi dcs write 1P(0x30, 0x02); mipi dsi dcs write 1P(0x03, 0x22); mipi\_dsi\_dcs\_write\_1P(0x04, 0x06); mipi dsi dcs write 1P(0x05, 0x66); mipi dsi dcs write 1P(0x06, 0x80); mipi\_dsi\_dcs\_write\_1P(0x08, 0x3C); mipi dsi dcs write seq(0x0B, 0x17, 0x1B, 0x03, 0x10, 0x11, 0x1F, 0x1D, 0x06, 0x08, 0x16, 0x03); mipi dsi dcs write seq(0x0C, 0x03, 0 0x03, 0x03); mipi dsi dcs write seq(0x0D, 0x05, 0x1A, 0x03, 0x10, 0x11, 0x1E, 0x1C, 0x07, 0x09, 0x0A, 0x03); mipi dsi dcs write seq(0x0E, 0x03, 0 0x03, 0x03); mipi dsi dcs write seq(0x0F, 0x0A, 0x1A, 0x03, 0x10, 0x11, 0x1C, 0x1E, 0x09, 0x07, 0x05, 0x03); mipi dsi dcs write seq(0x10, 0x03, 0 0x03, 0x03);mipi dsi dcs write seq(0x11, 0x16, 0x1B, 0x03, 0x10, 0x11, 0x1D, 0x1F, 0x08, 0x06, 0x17, 0x03); mipi dsi dcs write seq(0x12, 0x03, 0 0x03, 0x03);

WF70D5SWAHMNN0#

第33頁,共36頁

```

mipi dsi dcs write seq(0x13, 0x00, 0x00, 0x00, 0x00);

mipi dsi dcs write seq(0x14, 0x00, 0x00, 0x00, 0x00);

mipi dsi dcs write seq(0x15, 0x00, 0x00, 0x00, 0x00);

mipi_dsi_dcs_write_1P(0x17, 0x40);

mipi dsi dcs write 1P(0x18, 0x82);

mipi dsi dcs write 1P(0x30, 0x06);

mipi dsi dcs write seq(0x12, 0x3F, 0x29, 0x2B, 0x39, 0x26, 0x25, 0x26, 0x25, 0x23,

0x14, 0x29, 0x21, 0x17, 0x2A);

mipi dsi dcs write seq(0x13, 0x3F, 0x29, 0x2B, 0x39, 0x26, 0x25, 0x26, 0x25, 0x23,

0x14, 0x29, 0x21, 0x17, 0x2A);

mipi dsi dcs write 1P(0x30, 0x07);

mipi dsi dcs write 1P(0x00, 0x06);

mipi dsi dcs write 1P(0x0D, 0x01);

mipi dsi dcs write 1P(0x30, 0x08);

mipi dsi dcs write 1P(0x01, 0xB4);

mipi dsi dcs write 1P(0x30, 0x0A);

mipi dsi dcs write 1P(0x02, 0x4F);

mipi dsi dcs write 1P(0x0B, 0x40);

mipi dsi dcs write 1P(0x10, 0x82); // Z 改反 Z

mipi dsi dcs write 1P(0x13, 0x20); // 0x3A->0x20(减小 debug-20 度显示竖纹)

mipi dsi dcs write 1P(0x30, 0x0D);

mipi dsi dcs write 1P(0x0D, 0x04);

mipi dsi dcs write 1P(0x10, 0x0B);

mipi dsi dcs write 1P(0x11, 0x0B);

mipi dsi dcs write 1P(0x12, 0x0B);

mipi dsi dcs write 1P(0x13, 0x0B);

mipi dsi dcs write 1P(0x30, 0x00);

mipi_dsi_dcs_write_NP(0x11); // Sleep Out

delay m_s(120);

mipi dsi dcs write NP(0x29); // Display On

```

}

delay  $m_s(50)$ ;

#### LCM Sample Estimate Feedback Sheet winstar Module Number : Page: 1 **1** • <u>Panel Specification</u> : 1. Panel Type : □ Pass 🗆 NG ,\_\_\_\_\_ 🗆 NG ,\_\_\_\_\_ 2. View Direction : □ Pass 3 Numbers of Dots : □ Pass □ NG ,\_\_\_\_\_ 🗆 NG ,\_\_\_\_\_ 4. View Area : □ Pass 5 Active Area : □ Pass □ NG ,\_\_\_\_\_ 6. Operating □ Pass 🗆 NG ,\_\_\_\_\_ □ NG ,\_\_\_\_\_ 7. Storage Temperature : □ Pass 8. Others : 2 · Mechanical 1. PCB Size : □ Pass □ NG ,\_\_\_\_\_ 2. Frame Size : 🗆 NG ,\_\_\_\_\_ □ Pass 🗆 NG ,\_\_\_\_\_ 3 Material of Frame : □ Pass 4. Connector Position : □ NG ,\_\_\_\_\_ □ Pass 5. Fix Hole Position : □ NG ,\_\_\_\_\_ □ Pass 6. Backlight Position: □ NG ,\_\_\_\_\_ - Pass 🗆 NG ,\_\_\_\_\_ 7. Thickness of PCB: □ Pass 8. Height of Frame to 🗆 NG , □ Pass 9. Height of Module 3 Pass □ NG ,\_\_\_\_ □ NG ,\_\_\_\_\_ 10. Others : Pass 3 • Relative Hole Size : □ NG ,\_\_\_\_ 1. Pitch of Connector : Pass 2. Hole size of Connector : □ Pass □ NG , 3. Mounting Hole size : 🗆 NG ,\_\_\_\_\_ Pass 4. Mounting Hole Type : □ NG ,\_\_\_\_\_ □ Pass 5. Others : □ Pass □ NG ,\_\_\_\_\_ 4 · Backlight Specification : 1. B/L Type : □ NG , □ Pass 2. B/L Color : □ Pass □ NG ,\_\_\_\_\_ 3. B/L Driving Voltage (Reference for LED □ Pass □ NG ,\_\_\_\_\_ 4. B/L Driving Current : □ Pass □ NG , 🗆 NG ,\_\_\_\_\_ 5. Brightness of B/L : □ Pass 6. B/L Solder Method : □ Pass 🗆 NG ,\_\_\_\_\_ 7. Others : □ NG , □ Pass >> Go to page 2 <<

WF70D5SWAHMNN0#

第35頁,共36頁

Winstar Module Number <sup>;</sup> \_

Page: 2

| NOC        | aule Number :              |             |

|------------|----------------------------|-------------|

| <b>5</b> 、 | Electronic Characteristics | of Module : |

| 1.         | Input Voltage:             | □ Pass      |

| 2.         | Supply Current :           | □ Pass      |

| 3.         | Driving Voltage for LCD :  | Pass        |

| 4.         | Contrast for LCD :         | □ Pass      |

| 5.         | B/L Driving Method :       | □ Pass      |

| 6.         | Negative Voltage Output :  | Pass        |

| 7.         | Interface Function :       | □ Pass      |

| 8.         | LCD Uniformity :           | Pass        |

| 9.         | ESD test :                 | Pass        |

| 10.        | Others :                   | □ Pass      |

| 6、         | Summary :                  |             |

| Sales signature :  |     |

|--------------------|-----|

| Customer Signature | e : |

| Date : | 1 |  |  |

|--------|---|--|--|

|        |   |  |  |

WF70D5SWAHMNN0#

#### **Disclaimer**

ALL PRODUCTS, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Texim Europe B.V. its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Texim"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Texim makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product.

It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application.

Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time.

All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts.

Please contact us if you have any questions about the contents of the datasheet.

This may not be the latest version of the datasheet. Please check with us if a later version is available.

### Headquarters & Warehouse

Elektrostraat 17 NL-7483 PG Haaksbergen The Netherlands

| T:        | +31 (0)53 573 33 33   |

|-----------|-----------------------|

| E:        | info@texim-europe.com |

| Homepage: | www.texim-europe.com  |

#### The Netherlands

Elektrostraat 17 NL-7483 PG Haaksbergen

T: +31 (0)53 573 33 33 E: nl@texim-europe.com

### Belgium

Zuiderlaan 14, box 10 B-1731 Zellik

T: +32 (0)2 462 01 00 E: belgium@texim-europe.com

UK & Ireland

St Mary's House, Church Lane Carlton Le Moorland Lincoln LN5 9HS

T: +44 (0)1522 789 555 E: uk@texim-europe.com

**Germany** Bahnhofstrasse 92

D-25451 Quickborn

T: +49 (0)4106 627 07-0 E: germany@texim-europe.com

#### Germany

Martin-Kollar-Strasse 9 D-81829 München

T: +49 (0)89 436 086-0 E: muenchen@texim-europe.com

**Austria** Warwitzstrasse 9 A-5020 Salzburg

T: +43 (0)662 216 026 E: austria@texim-europe.com

**Nordic** Stockholmsgade 45 2100 Copenhagen

T: +45 88 20 26 30 E: nordic@texim-europe.com

Martin-Kollar-Strasse 9 D-81829 München

T: +49 (0)89 436 086-0 E: italy@texim-europe.com

2025

www.texim-europe.com