# WINSTAR Display Co.,Ltd. 華凌光電股份有限公司

# 1.54 inch E-paper Display Series

WAA0154A2ANA4NXXX000

# **Product Specifications**

| Customer    | Standard              |

|-------------|-----------------------|

| Description | 1.54" E-PAPER DISPLAY |

| Model Name  | WAA0154A2ANA4NXXX000  |

| Date        | 2024/07/10            |

| Revision    | 1.0                   |

|             | 1                     |

| D        | esign Engineerin | Ig     |

|----------|------------------|--------|

| Approval | Check            | Design |

|          |                  |        |

|          |                  |        |

|          |                  |        |

## **REVISION HISTORY**

| Rev | Date        | Item         | Page | Remark |

|-----|-------------|--------------|------|--------|

| 1.0 | Jul.10.2024 | New Creation | ALL  |        |

|     |             |              |      |        |

## CONTENTS

| 1. Over View                                      | 5   |

|---------------------------------------------------|-----|

| 2. Features                                       | 5   |

| 3. Mechanical Specifications                      | 5   |

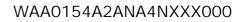

| 4. Mechanical Drawing of EPD module               | 6   |

| 5. Input /Output Pin Assignment                   | ·7  |

| 6. Command Table                                  | 9   |

| 7. Electrical Characteristics                     | 21  |

| 8. Optical Specifications                         | 27  |

| 9. Typical Application Circuit                    | -28 |

| 10. Matched Development Kit                       | 29  |

| 11. Reliability test                              | 30  |

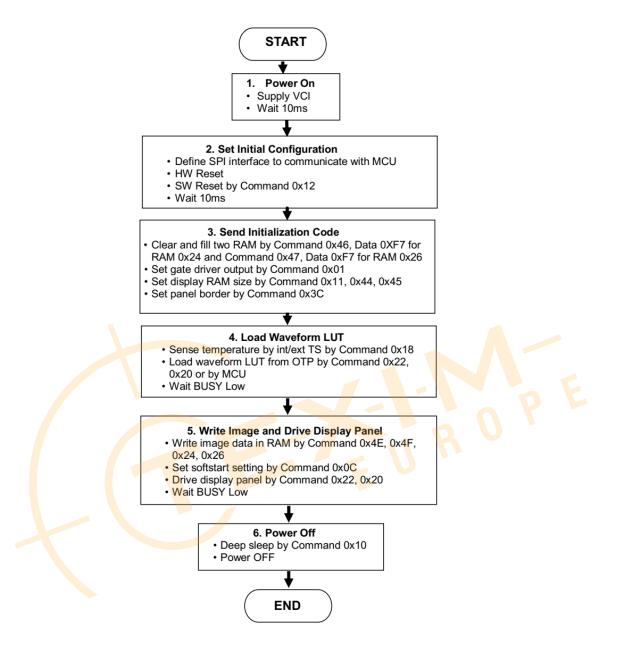

| 12. Typical Operating Sequence                    | 31  |

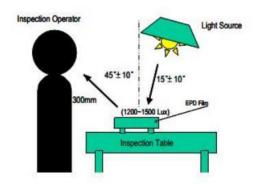

| 13. Inspection method and condition               | 32  |

| 14. Handling, Safety and Environment Requirements | 36  |

| 15. Packaging                                     | 37  |

| 16. Precautions                                   | -38 |

### **1. Over View**

WINSTAR

WAA0154A2ANA4NXXX000 is a TFT active matrix electrophoretic display, with interface and a reference system design. The 1.54" active area contains 200×200 pixels, and has 1-bit black/white full display capabilities. An integrated circuit contains gate buffer, source buffer, interface, timing control logic, oscillator, DC-DC, SRAM, LUT, VCOM and border are supplied with each panel.

## 2.Features

- High contrast

- High reflectance

- Ultra wide viewing angle

- Ultra low power consumption

- Pure reflective mode

- Bi-stable

- Commercial temperature range

- Landscape, portrait mode

- Antiglare hard-coated front-surface

- Low current sleep mode

- On chip display RAM

- Serial peripheral interface available

- On-chip oscillator

- On-chip booster and regulator control for generating VCOM, Gate and source driving voltage

- I2C Signal Master Interface to read external temperature sensor

- Available in COG package IC thickness 300um

## **3.Mechanical Specifications**

| Parameter           | Specifications            | Unit  | Remark  |

|---------------------|---------------------------|-------|---------|

| Screen Size         | 1.54                      | Inch  |         |

| Display Resolution  | 200(H)×200(V)             | Pixel | Dpi:184 |

| Active Area         | 27.0(H)×27.0(V)           | mm    |         |

| Pixel Pitch         | 0.14×0.14                 | mm    |         |

| Pixel Configuration | Square                    |       |         |

| Outline Dimension   | 31.80(H)×37.32(V) ×1.0(D) | mm    |         |

| Weight              | 2.18±0.5                  | g     |         |

## 4. Mechanical Drawing of EPD module

## **5. Input /Output Pin Assignment**

| No. | Name  | I/O | Description                                                                                                              | Remark    |

|-----|-------|-----|--------------------------------------------------------------------------------------------------------------------------|-----------|

| 1   | NC    |     | Do not connect with other NC pins                                                                                        | Keep Open |

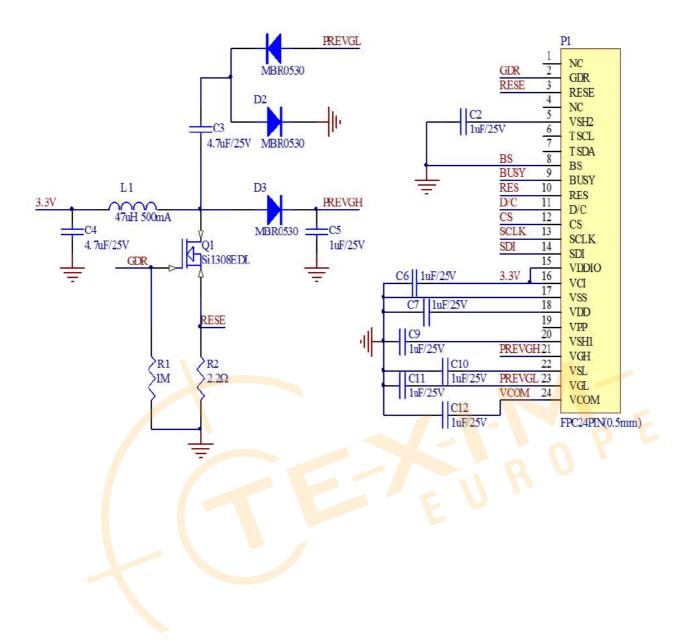

| 2   | GDR   | 0   | N-Channel MOSFET Gate Drive Control                                                                                      |           |

| 3   | RESE  | Ι   | Current Sense Input for the Control Loop                                                                                 |           |

| 4   | NC    | NC  | Do not connect with other NC pins                                                                                        | Keep Open |

| 5   | VSH2  | С   | Positive Source driving voltage(Red)                                                                                     |           |

| 6   | TSCL  | 0   | I <sup>2</sup> C Interface to digital temperature sensor Clock pin                                                       |           |

| 7   | TSDA  | I/O | I <sup>2</sup> C Interface to digital temperature sensor Data pin                                                        |           |

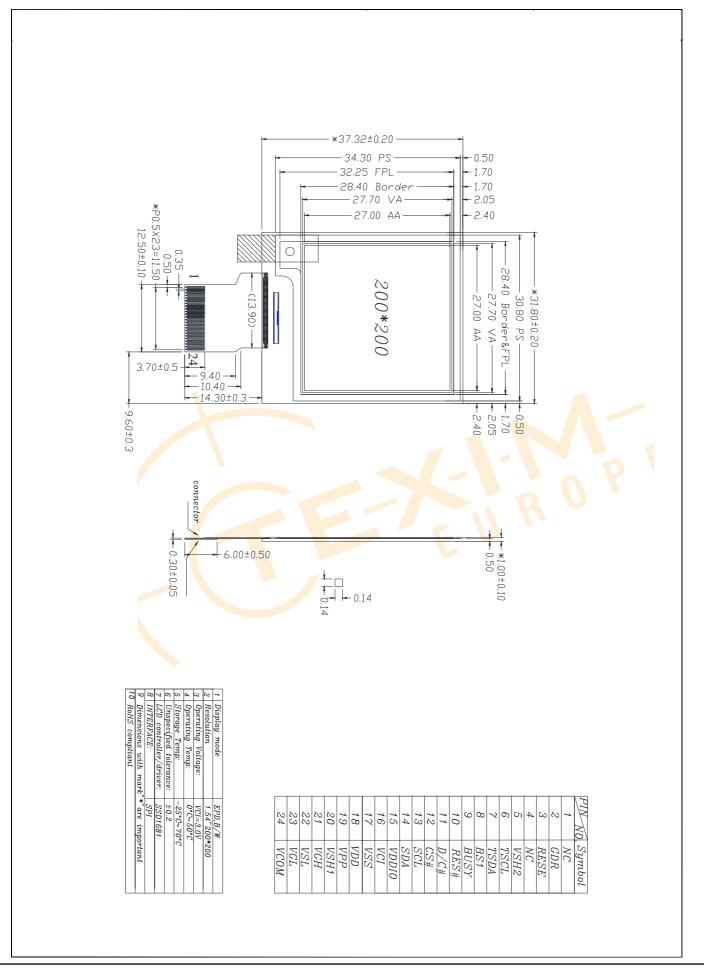

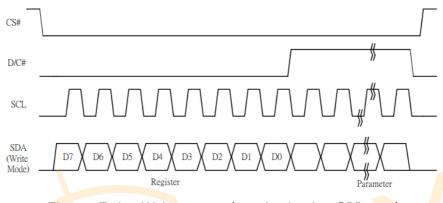

| 8   | BS1   | Ι   | Bus Interface selection pin                                                                                              | Note 5-5  |

| 9   | BUSY  | 0   | Busy state output pin                                                                                                    | Note 5-4  |

| 10  | RES#  | Ι   | Reset signal input. Active Low.                                                                                          | Note 5-3  |

| 11  | D/C#  | Ι   | Data /Command control pin                                                                                                | Note 5-2  |

| 12  | CS#   | Ι   | Chip select input pin                                                                                                    | Note 5-1  |

| 13  | SCL   | Ι   | Serial Clock pin (SPI)                                                                                                   | Y         |

| 14  | SDA   | Ι   | Serial Data pin (SPI)                                                                                                    |           |

| 15  | VDDIO | Р   | Power Supply for interface logic pins It should be connected with VCI                                                    |           |

| 16  | VCI   | Р   | Power Supply for the chip                                                                                                |           |

| 17  | VSS   | Р   | Ground                                                                                                                   |           |

| 18  | VDD   | С   | Core logic power pin VDD can be regulated<br>internally from VCI. A capacitor should be<br>connected between VDD and VSS |           |

| 19  | VPP   | Р   | FOR TEST                                                                                                                 |           |

| 20  | VSH1  | С   | Positive Source driving voltage                                                                                          |           |

| 21  | VGH   | С   | Power Supply pin for Positive Gate driving voltage<br>and VSH1                                                           |           |

| 22  | VSL   | С   | Negative Source driving voltage                                                                                          |           |

| 23  | VGL   | С   | Power Supply pin for Negative Gate driving voltage<br>VCOM and VSL                                                       |           |

| 24  | VCOM  | С   | VCOM driving voltage                                                                                                     |           |

**Note 5-1**: This pin (CS#) is the chip select input connecting to the MCU. The chip is enabled for MCU communication only when CS# is pulled Low.

**Note 5-2**: This pin (D/C#) is Data/Command control pin connecting to the MCU. When the pin

is pulled High, the data will be interpreted as data. When the pin is pulled Low, the data will be interpreted as command.

**Note 5-3**: This pin (RES#) is reset signal input. The Reset is active low.

**Note 5-4**: This pin (BUSY) is Busy state output pin. When Busy is High, the operation of chip should not be interrupted and any commands should not be issued to the module. The driver IC will put Busy pin High when the driver IC is working such as:

Outputting display waveform; or

Communicating with digital temperature sensor

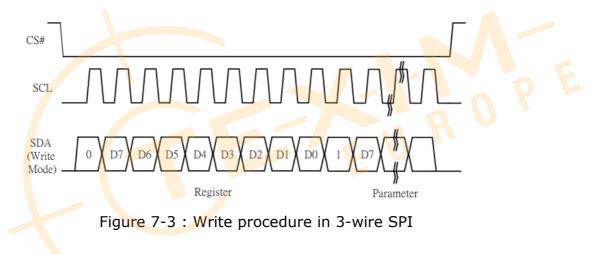

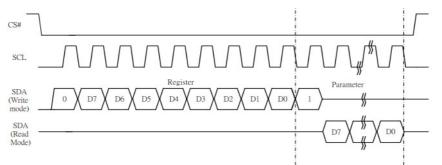

**Note 5-5**: This pin (BS1) is for 3-line SPI or 4-line SPI selection. When it is "Low", 4-line SPI is selected. When it is "High", 3-line SPI (9 bits SPI) is selected. Please refer to below Table.

| BS1 State | MCU Interface                                          |

|-----------|--------------------------------------------------------|

| L         | 4-lines serial peripheral interface(SPI) - 8 bits SPI  |

| Н         | 3- lines serial peripheral interface(SPI) - 9 bits SPI |

## 6. Command Table

| Com  | man  | d Tal | ole            |                |                |                |                |                |                |                      |                       |                                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                          |                                                                                            |            |

|------|------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|

| R/W# | D/C# | Hex   | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0                   | Command               | Descripti                                                                                                                                                                                                                     | on                                                                                                                                        |                                                                                                          |                                                                                            |            |

| 0    | 0    | 01    | 0              | 0              | 0              | 0              | 0              | 0              | 0              | 1                    | Driver Output control | Gate setti                                                                                                                                                                                                                    | ng                                                                                                                                        |                                                                                                          |                                                                                            |            |

| 0    | 1    |       | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub>       |                       | A[8:0]= C                                                                                                                                                                                                                     |                                                                                                                                           |                                                                                                          |                                                                                            |            |

| 0    | 1    |       |                |                |                |                |                |                | 0              | A                    | -                     | MUX Gate                                                                                                                                                                                                                      | e lines set                                                                                                                               | ting as (A                                                                                               | [8:0] + 1)                                                                                 | .          |

| 0    | 1    |       | 0              | 0              | 0              | 0              | 0              | 0<br>B2        | 0<br>B1        | A <sub>8</sub><br>Bo |                       | B[2:0] = 0<br>Gate scar<br>B[2]: GD<br>Selects th<br>GD=0 [PC<br>G0 is the<br>output sec<br>GD=1,<br>G1 is the<br>output sec<br>B[1]: SM<br>Change s<br>SM=0 [PC<br>G0, G1, C<br>interlaced<br>SM=1,<br>G0, G2, C<br>B[0]: TB | 00 [POR]<br>nning sequence<br>DR],<br>1st gate of<br>quence is<br>1st gate of<br>quence is<br>canning of<br>DR],<br>52, G31<br>)<br>54G19 | out Gate<br>output cha<br>G0,G1, G<br>output cha<br>G1, G0, C<br>order of ga<br>99 (left ar<br>8, G1, G3 | I direction<br>nnel, gate<br>2, G3,<br>nnel, gate<br>33, G2,<br>ite driver.<br>nd right ga | e<br>e<br> |

|      |      |       |                |                |                |                |                |                |                |                      |                       | TB = 0 [P<br>TB = 1, so                                                                                                                                                                                                       |                                                                                                                                           |                                                                                                          |                                                                                            | <b>X</b>   |

|      |      |       |                |                | ~              |                |                |                |                |                      |                       |                                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                          |                                                                                            |            |

| 0    | 0    | 03    | 0              | 0              | 0              | 0              | 0              | 0              | 1              | 1                    | Gate Driving voltage  | Set Gate<br>A[4:0] = 0                                                                                                                                                                                                        |                                                                                                                                           |                                                                                                          |                                                                                            |            |

| 0    | 1    |       | 0              | 0              | 0              | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub>       | Control               | VGH setti                                                                                                                                                                                                                     |                                                                                                                                           |                                                                                                          |                                                                                            |            |

|      |      |       |                |                |                |                |                |                |                |                      |                       | A[4:0]                                                                                                                                                                                                                        | VGH                                                                                                                                       | A[4:0]                                                                                                   | VGH                                                                                        |            |

|      |      |       |                |                |                |                |                |                | •              |                      |                       | 00h                                                                                                                                                                                                                           | 20                                                                                                                                        | 0Dh                                                                                                      | 15                                                                                         | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 03h                                                                                                                                                                                                                           | 10                                                                                                                                        | 0Eh                                                                                                      | 15.5                                                                                       | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 04h                                                                                                                                                                                                                           | 10.5                                                                                                                                      | 0Fh                                                                                                      | 16                                                                                         | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 05h                                                                                                                                                                                                                           | 11                                                                                                                                        | 10h                                                                                                      | 16.5                                                                                       | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 06h                                                                                                                                                                                                                           | 11.5                                                                                                                                      | 11h                                                                                                      | 17                                                                                         | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 07h                                                                                                                                                                                                                           | 12                                                                                                                                        | 12h                                                                                                      | 17.5                                                                                       | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 08h                                                                                                                                                                                                                           | 12.5                                                                                                                                      | 13h                                                                                                      | 18                                                                                         | 1          |

|      |      |       |                | -              |                |                |                |                |                |                      |                       | 07h                                                                                                                                                                                                                           | 12                                                                                                                                        | 14h                                                                                                      | 18.5                                                                                       | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 08h                                                                                                                                                                                                                           | 12.5                                                                                                                                      | 15h                                                                                                      | 19                                                                                         | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 09h                                                                                                                                                                                                                           | 13                                                                                                                                        | 16h                                                                                                      | 19.5                                                                                       | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 0Ah                                                                                                                                                                                                                           | 13.5                                                                                                                                      | 17h                                                                                                      | 20                                                                                         | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 0Bh                                                                                                                                                                                                                           | 14                                                                                                                                        | Other                                                                                                    | NA                                                                                         | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       | 0Ch                                                                                                                                                                                                                           | 14.5                                                                                                                                      |                                                                                                          |                                                                                            | 1          |

|      |      |       |                |                |                |                |                |                |                |                      |                       |                                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                          |                                                                                            | -          |

|      |      |       |                |                |                |                |                |                |                |                      |                       |                                                                                                                                                                                                                               |                                                                                                                                           |                                                                                                          |                                                                                            |            |

| Com  | man           | d Tal | ble            |                |                |                |                       |                |                 |                |              |                       |              |                                                       |

|------|---------------|-------|----------------|----------------|----------------|----------------|-----------------------|----------------|-----------------|----------------|--------------|-----------------------|--------------|-------------------------------------------------------|

|      | D/C#          |       |                | D6             | D5             | D4             | D3                    | D2             | D1              | D0             | Comn         | nand                  |              | Description                                           |

| 0    | 0             | 04    | 0              | 0              | 0              | 0              | 0                     | 1              | 0               | 0              | Sourc        | e Driving             | voltage      | Set Source driving voltage                            |

| 0    | 1             |       | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>        | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | Contro       | -                     |              | A[7:0] = 41h [POR], VSH1 at 15V                       |

| 0    | 1             |       | B <sub>7</sub> | B <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub>        | B <sub>2</sub> | B <sub>1</sub>  | Bo             | 1            |                       |              | B[7:0] = A8h [POR], VSH2 at 5V.                       |

| 0    | 1             |       | C <sub>7</sub> |                | C5             | C4             | <b>C</b> <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub>  | C <sub>0</sub> | -            |                       |              | C[7:0] = 32h [POR], VSL at -15V<br>Remark: VSH1>=VSH2 |

| -    | <br> /B[7]    | - 1   | 07             | 06             | 05             | 04             | 03                    |                |                 |                |              |                       |              | C[7] = 0,                                             |

| VS   | H1/V          |       | /oltag         | je se          | tting          | from           | 2.4V                  | VS             |                 |                |              | e setting             | from 9V      | VSL setting from -5V to -17V                          |

| to 8 | .8V<br>B[7:0] | Veh   | 1/VSH2         |                | 3[7:0]         | VSH1           | /VSH2                 |                | 17V<br>A/B[7:0] |                | H1/VSH2      | A/B[7:0]              | VSH1/VSH     | 2 C[7:0] VSL                                          |

|      | 8Eh           | -     | 2.4            |                | Fh             |                | .7                    |                | 23h             |                | 9            | 3Ch                   | 14           | 2 C[7:0] VSL<br>0Ah -5                                |

|      | 8Fh           |       | 2.5            |                | 80h            |                | .8                    |                | 24h             |                | 9.2          | 3Dh                   | 14.2         | 0Ch -5.5                                              |

|      | 90h<br>91h    |       | 2.6<br>2.7     |                | 81h<br>82h     |                | .9<br>6               |                | 25h<br>26h      | _              | 9.4<br>9.6   | 3Eh<br>3Fh            | 14.4<br>14.6 | 0Eh -6                                                |

|      | 92h           | _     | 2.8            |                | 33h            |                | .1                    |                | 27h             |                | 9.8          | 40h                   | 14.8         | 10h -6.5                                              |

|      | 93h           | _     | 2.9            |                | 34h            |                | .2                    |                | 28h             |                | 10           | 41h                   | 15           | 12h -7                                                |

|      | 94h           | +     | 3              | +              | 85h            |                | .3                    |                | 29h             |                | 10.2         | 42h                   | 15.2         | 14h -7.5<br>16h -8                                    |

|      | 95h<br>96h    | _     | 3.1<br>3.2     |                | 86h<br>87h     |                | .4                    |                | 2Ah<br>2Bh      | _              | 10.4<br>10.6 | 43h<br>44h            | 15.4<br>15.6 |                                                       |

|      | 97h           |       | 3.3            |                | 38h            |                | .6                    |                | 2Ch             |                | 10.8         | 45h                   | 15.8         | 1Ah9                                                  |

|      | 98h           |       | 3.4            |                | 89h            |                | .7                    |                | 2Dh             |                | 11           | 46h                   | 16           | 1Ch -9.5                                              |

|      | 99h<br>9Ah    |       | 3.5<br>3.6     |                | Bh             |                | .8<br>.9              | $  \vdash$     | 2Eh<br>2Fh      | _              | 11.2<br>11.4 | 47h<br>48h            | 16.2<br>16.4 | 1Eh -10                                               |

|      | 9An<br>9Bh    | _     | 3.7            | <u> </u>       | Ch             |                | 7                     |                | 30h             |                | 11.4         | 40n<br>49h            | 16.4         | 20h -10.5                                             |

|      | 9Ch           |       | 3.8            |                | Dh             |                | .1                    |                | 31h             |                | 11.8         | 4Ah                   | 16.8         | 22h -11                                               |

|      | 9Dh           | _     | 3.9            |                | Eh             |                | .2                    |                | 32h             | _              | 12           | 4Bh                   | 17           | 24h -11.5                                             |

|      | 9Eh<br>9Fh    |       | 4              |                | 8Fh<br>C0h     |                | .3<br>.4              |                | 33h<br>34h      | _              | 12.2<br>12.4 | Other                 | NA           | 26h -12<br>28h -12.5                                  |

|      | A0h           |       | 4.2            |                | 21h            |                | .5                    |                | 35h             |                | 12.6         |                       |              | 2011 -12.3<br>2Ah -13                                 |

|      | A1h           | _     | 4.3            |                | 2h             |                | .6                    |                | 36h             |                | 12.8         |                       |              | 2Ch -13.5                                             |

|      | A2h           | -     | 4.4            |                | C3h            | -              | .7                    |                | 37h             | _              | 13           |                       |              | 2Eh -14                                               |

|      | A3h<br>A4h    |       | 4.5<br>4.6     |                | 24h<br>25h     | -              | .8                    |                | 38h<br>39h      |                | 13.2<br>13.4 |                       |              | 30h -14.5                                             |

|      | A5h           |       | 4.7            |                | C6h            |                | 8                     |                | 3Ah             |                | 13.6         |                       |              | 32h -15                                               |

|      | A6h           | _     | 4.8            | -              | C7h            | _              | .1                    |                | 3Bh             |                | 13.8         |                       |              | 34h -15.5                                             |

|      | A7h<br>A8h    |       | 4.9<br>5       |                | 28h<br>29h     | _              | .2                    |                |                 |                |              |                       |              | 36h -16<br>38h -16.5                                  |

|      | A9h           |       | 5.1            |                | Ah             |                | .4                    |                |                 |                |              |                       |              | 301 -10.5<br>3Ah -17                                  |

|      | AAh           | -     | 5.2            | +              | Bh             | -              | .5                    |                |                 |                |              |                       |              | Other NA                                              |

|      | ABh           |       | 5.3            | -              | Ch             | -              | .6                    |                |                 |                |              |                       |              |                                                       |

|      | ACh<br>ADh    |       | 5.4<br>5.5     | -              | Dh<br>Eh       |                | .7                    |                |                 |                |              |                       |              |                                                       |

|      | AEh           | _     | 5.6            |                | ther           | -              | IA                    |                |                 |                |              |                       |              |                                                       |

|      |               |       |                |                |                |                |                       |                |                 |                |              |                       |              |                                                       |

|      |               |       |                |                |                |                |                       |                |                 |                |              |                       |              |                                                       |

| 0    | 0             | 08    | 0              | 0              | 0              | 0              | 1                     | 0              | 0               | 0              |              | Code Set<br>Program   | ting         | Program Initial Code Setting                          |

|      |               |       |                |                |                |                |                       |                |                 |                |              | -                     |              | The command required CLKEN=1.                         |

|      |               |       |                |                |                |                |                       |                |                 |                |              |                       |              | Refer to Register 0x22 for detail.                    |

|      |               |       |                |                |                |                |                       |                |                 |                |              |                       |              | BUSY pad will output high during                      |

|      |               |       |                |                |                |                |                       |                |                 |                |              |                       |              | operation.                                            |

| 0    | 0             | 09    | 0              | 0              | 0              | 0              | 1                     | 0              | 0               | 1              | Write        | Register f            | or Initial   | Write Register for Initial Code Setting               |

|      | 1930          | 03    | 1000           |                |                | (26))<br>      |                       | 1000           |                 | _              |              | Setting               | or mud       | Selection                                             |

| 0    | 1             |       | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub>        | A <sub>2</sub> | A <sub>1</sub>  | A <sub>0</sub> | -            | County                |              | A[7:0] ~ D[7:0]: Reserved                             |

| 0    | 1             |       | B <sub>7</sub> | B <sub>6</sub> | B <sub>5</sub> | B <sub>4</sub> | B <sub>3</sub>        | B <sub>2</sub> | B <sub>1</sub>  | B <sub>0</sub> |              |                       |              | Details refer to Application Notes of Initial         |

| 0    | 1             |       | C7             | C <sub>6</sub> | <b>C</b> 5     | C <sub>4</sub> | C <sub>3</sub>        | C <sub>2</sub> | C <sub>1</sub>  | C <sub>0</sub> |              |                       |              | Code Setting                                          |

| 0    | 1             |       | D <sub>7</sub> | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub>        | D <sub>2</sub> | D <sub>1</sub>  | D <sub>0</sub> |              |                       |              |                                                       |

|      |               |       |                |                |                |                |                       |                |                 |                |              |                       |              |                                                       |

| 0    | 0             | 0A    | 0              | 0              | 0              | 0              | 1                     | 0              | 1               | 0              |              | Register f<br>Setting | for Initial  | Read Register for Initial Code Setting                |

|      |               |       |                |                |                |                |                       |                | 1               |                |              |                       |              | <u> </u>                                              |

| <b>R/W#</b> | D/C# | Hex | D7 | D6             | D5             | D4                    | D3             | D2             | D1             | DO             | Command            | Description                 |                                                                                                               |

|-------------|------|-----|----|----------------|----------------|-----------------------|----------------|----------------|----------------|----------------|--------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------|

| 0           | •    |     |    |                |                |                       |                |                |                |                |                    | Description                 |                                                                                                               |

|             | 0    | 0C  | 0  | 0              | 0              | 0                     | 1              | 1              | 0              | 0              | Booster Soft start |                             | vith Phase 1, Phase 2 and Phase 3<br>ent and duration setting.                                                |

| 0           | 1    |     | 1  | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub>        | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Control            |                             |                                                                                                               |

| 0           | 1    |     | 1  | B <sub>6</sub> | B <sub>5</sub> | <b>B</b> <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo             |                    | A[7:0] -> Soft sta<br>= 8Bh | rt setting for Phase1                                                                                         |

| 0           | 1    |     | 1  | C <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub>        | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> |                    | B[7:0] -> Soft sta          | rt setting for Phase2                                                                                         |

| 0           | 1    |     | 0  | 0              | D <sub>5</sub> | D <sub>4</sub>        | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | Do             | -                  | = 9Ch                       | [POR]<br>rt setting for Phase3                                                                                |

|             |      |     |    |                |                |                       |                |                |                |                |                    | = 96h (                     | [POR]                                                                                                         |

|             |      |     |    |                |                |                       |                |                |                |                |                    | D[7:0] -> Duration<br>= 0Fh |                                                                                                               |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | tion of each byte:                                                                                            |

|             |      |     |    |                |                |                       |                |                |                |                |                    | Bit[6:4]                    | Driving Strength                                                                                              |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | Selection                                                                                                     |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 000                         | 1(Weakest)                                                                                                    |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 001                         | 2                                                                                                             |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 010                         | 3                                                                                                             |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 011                         | 4<br>5                                                                                                        |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 100                         | 6                                                                                                             |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 101                         | 7                                                                                                             |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 110                         | 8(Strongest)                                                                                                  |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | o(Guongeat)                                                                                                   |

|             |      |     |    |                |                |                       |                |                |                |                |                    | Bit[3:0]                    | Min Off Time Setting of GDR<br>[ Time unit ]                                                                  |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 0000                        | [ Time unit ]                                                                                                 |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | NA                                                                                                            |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 0011                        | 2.6                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 0101                        | 3.2                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 0110                        | 3.9                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 0111                        | 4.6                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1000                        | 5.4                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1001                        | 6.3                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1010                        | 7.3                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1011                        | 8.4                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1100                        | 9.8                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1101                        | 11.5                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1110                        | 13.8                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 1111                        | 16.5                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | D[5:4]: du<br>D[3:2]: du    | ation setting of phase<br>ration setting of phase 3<br>ration setting of phase 2<br>ration setting of phase 1 |

|             |      |     |    |                |                |                       |                |                |                |                |                    | Bit[1:0]                    | Duration of Phase<br>[Approximation]                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 00                          | 10ms                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 01                          | 20ms                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 10                          | 30ms                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 11                          | 40ms                                                                                                          |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             |                                                                                                               |

| 0           | 0    | 10  | 0  | 0              | 0              | 1                     | -              | -              | 0              |                | eep Sleep mode     | Deep Sleep m                |                                                                                                               |

| 0           | 1    |     | 0  | 0              | 0              | 0                     | 0              | 0              | A1             | A <sub>0</sub> |                    |                             | scription                                                                                                     |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | rmal Mode [POR]                                                                                               |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | ter Deep Sleep Mode 1                                                                                         |

|             |      |     |    |                |                |                       |                |                |                |                |                    | 11 Ent                      | ter Deep Sleep Mode 2                                                                                         |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | mand initiated, the chip will                                                                                 |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | eep Mode, BUSY pad will                                                                                       |

|             |      |     |    |                |                |                       |                |                |                |                |                    | keep output hi              | gh.                                                                                                           |

|             |      |     |    |                |                |                       |                |                |                |                |                    | Remark:                     |                                                                                                               |

|             |      |     |    |                |                |                       |                |                |                |                |                    |                             | Sleep mode, User required                                                                                     |

| Com  | mane | d Ta | ble             |                 |                |                |                |                |                |                |                       |                                                                                                                                                                                                                                                                                                                                                       |

|------|------|------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W# | D/C# | Hex  | D7              | D6              | D5             | D4             | D3             | D2             | D1             | D0             | Command               | Description                                                                                                                                                                                                                                                                                                                                           |

| 0    | 0    | 14   | 0               | 0               | 0              | 1              | 0              | 1              | 0              | 0              | HV Ready Detection    | HV ready detection<br>A[7:0] = 00h [POR]<br>The command required CLKEN=1 and<br>ANALOGEN=1.<br>Refer to Register 0x22 for detail.<br>After this command initiated, HV Ready<br>detection starts.<br>BUSY pad will output high during<br>detection.<br>The detection result can be read from the<br>Status Bit Read (Command 0x2F).                    |

| 0    | 1    |      | 0               | A <sub>6</sub>  | A5             | A4             | 0              | A <sub>2</sub> | A <sub>1</sub> | Ao             |                       | A[6:4]=n for cool down duration:<br>10ms x (n+1)<br>A[2:0]=m for number of Cool Down Loop<br>to detect.<br>The max HV ready duration is<br>10ms x (n+1) x (m)<br>HV ready detection will be trigger after<br>each cool down time. The detection will be<br>completed when HV is ready.<br>For 1 shot HV ready detection, A[7:0] can<br>be set as 00h. |

| 0    | 0    | 15   | 0               | 0               | 0              | 1              | 0              | 1              | 0              | 1              | VCI Detection         | VCI Detection                                                                                                                                                                                                                                                                                                                                         |

| 0    | 1    | 15   | 0               | 0               | 0              | 0              | 0              | 1<br>A2        | 0<br>A1        | A <sub>0</sub> | VCI Detection         | A[2:0] = 100 [POR] , Detect level at 2.3V           A[2:0] : VCI level Detect           A[2:0] : VCI level Detect           011         2.2V           100         2.3V           101         2.4V           110         2.5V           111         2.6V                                                                                              |

|      |      |      |                 |                 |                |                |                |                |                |                |                       | Other     NA       Other     NA       The command required CLKEN=1 and ANALOGEN=1       Refer to Register 0x22 for detail.                                                                                                                                                                                                                            |

|      |      |      |                 |                 |                |                |                |                |                |                |                       | After this command initiated, VCI<br>detection starts.<br>BUSY pad will output high during<br>detection.<br>The detection result can be read from the<br>Status Bit Read (Command 0x2F).                                                                                                                                                              |

| 0    | 0    | 18   | 0               | 0               | 0              | 1              | 1              | 0              | 0              | 0              | Temperature Sensor    | Temperature Sensor Selection                                                                                                                                                                                                                                                                                                                          |

| 0    | 1    |      | A <sub>7</sub>  | A <sub>6</sub>  | A <sub>5</sub> | A4             | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A              | Control               | A[7:0] = 48h [POR], external temperatrure<br>sensor<br>A[7:0] = 80h Internal temperature sensor                                                                                                                                                                                                                                                       |

| 0    | 0    | 1A   | 0               | 0               | 0              | 1              | 1              | 0              | 1              | 0              | Temperature Sensor    | Write to temperature register.                                                                                                                                                                                                                                                                                                                        |

| 0    | 1    |      | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | Control (Write to     | A[11:0] = 7FFh [POR]                                                                                                                                                                                                                                                                                                                                  |

| 0    | 1    |      | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub> | A <sub>0</sub> | 0              | 0              | 0              | 0              | temperature register) |                                                                                                                                                                                                                                                                                                                                                       |

| 0    | 0    | 1B   | 0               | 0               | 0              | 1              | 1              | 0              | 1              | 1              | Temperature Sensor    | Read from temperature register.                                                                                                                                                                                                                                                                                                                       |

| 1    | 1    |      | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub> | A <sub>8</sub> | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | Control (Read from    |                                                                                                                                                                                                                                                                                                                                                       |

| 1    | 1    |      | A <sub>3</sub>  | A <sub>2</sub>  | A <sub>1</sub> | A <sub>0</sub> | 0              | 0              | 0              | 0              | temperature register) |                                                                                                                                                                                                                                                                                                                                                       |

| 0    | 0    | 12   | 0               | 0               | 0              | 1              | 0              | 0              | 1              | 0              | SW RESET              | It resets the commands and parameters to<br>their S/W Reset default values except<br>R10h-Deep Sleep Mode<br>During operation, BUSY pad will output<br>high.<br>Note: RAM are unaffected by this<br>command.                                                                                                                                          |

|      |      | d Ta |                |                |                |                |                |                |                |                |                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|------|------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ₹/W# | D/C# | Hex  | D7             | D6             | D5             | D4             | D3             | D2             | D1             | D0             | Command                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0    | 0    | 1C   | 0              | 0              | 0              | 1              | 1              | 1              | 0              | 0              | Temperature Sensor      | Write Command to External temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0    | 1    |      | A <sub>7</sub> | A <sub>6</sub> | A <sub>5</sub> | A <sub>4</sub> | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Control (Write Command  | sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0    | 1    |      | B <sub>7</sub> | B <sub>6</sub> | B5             | B <sub>4</sub> | B <sub>3</sub> | B <sub>2</sub> | B <sub>1</sub> | Bo             | to External temperature | A[7:0] = 00h [POR],                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0    | 1    |      | C <sub>7</sub> | C <sub>6</sub> | C <sub>5</sub> | C <sub>4</sub> | C <sub>3</sub> | C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> | sensor)                 | B[7:0] = 00h [POR],<br>C[7:0] = 00h [POR],                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |