# **IP3023<sup>™</sup> Wireless Network Processor**

Eight-Way Multithreaded Processor Optimized for Network Connectivity

# 1.0 Product Highlights

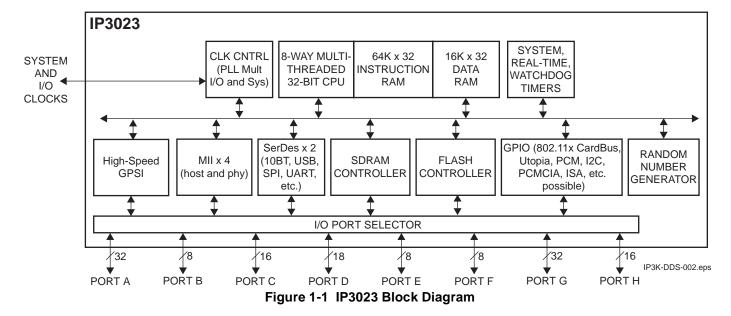

The IP3023<sup>™</sup> wireless network processor is a revolutionary new platform from Ubicom designed to provide highly integrated solutions for applications at the "edge" of Internet connectivity, including 802.11a/b/g access points, routers, hot spots, bridges, gateways, and a wide variety of embedded networked client solutions. The IP3023 is optimized for efficient network processing in embedded solutions. Its development has led to the definition of a new microprocessor architecture: Multithreaded Architecture for Software I/O (MASI). Many MASI concepts were pioneered in the Ubicom IP2000™ family of processors, but the IP3023 dramatically extends those techniques by introducing hardware support for multiple threads operating with no context switching overhead, as well as three-operand and memory-tomemory operations.

The IP3023 is a 250- or 325-MIPS 32-bit CPU supporting eight-way multithreaded operation. It provides for up to eight real-time tasks to execute in a completely deterministic fashion. In essence, the IP3023 supports running a different thread on every clock, but without the overhead for context switching typical with traditional microprocessor architectures. To the system designer, the IP3023 appears as if there were eight processors on the chip.

#### Key Features:

- 32-bit Mutithreaded CPU, in 250 MIPS and 325 MIPS versions

- IP3023 is optimized for wireless networking

- Eight-way simultaneous multithreading

- Deterministic execution on all threads

- Zero overhead full context switching

- Programmable MIPS per thread

- Optimized ISA for packet processing

- Memory-to-memory architecture, powerful addressing modes

- Small, fast instruction set, strong bit manipulation

- Reduced code size vs. RISC CPUs

- On-chip program and data memory

- Eliminates cache miss penalties

- 256 KB (64K x 32) of program SRAM

- 64 KB (16K x 32) of data SRAM

- Highly configurable I/O support

- Many combinations of software I/O:

- Utopia, PCMCIA, IDE/ATAPI

- PCM Highway, UART, SPI, I<sup>2</sup>C

- 32-bit 802.11a/g radios interface

- Up to 4 MII ports of 10/100 PHY

- Two SerDes for fast serial I/O:

- 10Base-T (MAC/PHY), USB, GPSI

- SPI, UART, two-wire serial, BlueRF

- High-speed GPSI port

- Additional key hardware

- True random number generator for software-implemented encryption/security (32-bit seed)

- Fixed-point MAC (16x16+48-bit, 250/325 MMACs) for voice/audio codecs, other signal processing tasks

- Independent I/O and core CPU clocking

- Separate phase-locked loops (PLLs)

- Programmable multipliers & dividers

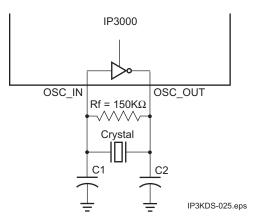

- Single low-cost crystal (10–20 MHz)

The multithreaded and deterministic nature of the IP3023 processor provides for integration of numerous functions on chip – some with on-chip hardware assist and some entirely in software – as threads, including the ability to support interfaces such as 10/100 MII and 10Base-T Ethernet MAC/PHY, USB, GPSI, Utopia, PCMCIA, IDE, PCM Highway, and CardBus/Mini PCI interface specific for 802.11a/g wireless radios. This yields both a high degree of flexibility and reduces die size, as it eliminates the need for many on-chip dedicated hardware blocks for specific functions.

The IP3023 employs a three-operand and memory-tomemory architecture, utilizing on-chip program and data memory support. This scheme enables highly efficient data movement and processing on data. The result is that the IP3023 is designed to support packet processing and transfers at wire speeds, eliminating the need for caches and large data buffers typically found in use with traditional RISC-based microprocessors.

To further optimize the IP3023 for networking infrastructure and embedded client solutions, the processor includes several key hardware support blocks, including true random number generator and fixed-point multiply/accumulate (MAC) units. The random number generator facilitates robust software implementation of common encryption/security protocols critical to the continued growth of wireless networking. The MAC unit supports implementation of voice/audio codecs and other signal processing tasks.

|                       | duct Highlights                                                                                   |

|-----------------------|---------------------------------------------------------------------------------------------------|

| 1.1<br>1.2            | Additional Features                                                                               |

| 1.3                   | Architecture                                                                                      |

| 1.3.1<br>1.3.2        | CPU                                                                                               |

| 1.3.3                 | CPU Data Memory                                                                                   |

| 1.3.4                 | Clocks, Frequency, and Timers                                                                     |

| 1.3.5<br>1.3.6        | Reduced Power Operation         6           Interrupts         6                                  |

| 1.3.7                 | Reset                                                                                             |

| 1.3.8                 | Programming and Debugging                                                                         |

| 1.3.9                 | Other Supported Functions                                                                         |

| 2.0 Pin<br>2.1        | Definitions         7           228-Pin BGA         7                                             |

| 2.1                   | Pin Descriptions                                                                                  |

| 2.2<br>2.3            | I/O Ports Signal Maps                                                                             |

|                       | stem Architecture 13                                                                              |

| 3.1                   | CPU Registers                                                                                     |

| 3.1.1<br>3.1.2        | Per-Thread Registers                                                                              |

| 3.2                   | Addressing Model                                                                                  |

| 3.3                   | Instruction Model                                                                                 |

| 3.4<br>3.5            | Fast Context Switch For Multithreading       17         Instruction Level Multithreading       17 |

| 3.5.1                 | Scheduling Table (HRT)                                                                            |

| 3.5.2                 | Scheduling Policies                                                                               |

| 3.5.3<br>3.5.4        | Schedulable Threads                                                                               |

| 3.5.5                 | Round-Robin (NRT) Scheduling                                                                      |

| 3.5.6                 | Suspend                                                                                           |

| 3.5.7                 | Startup                                                                                           |

| 3.6<br>3.7            | Programming and Debugging Support                                                                 |

| 3.7.1                 | Single-Step 19                                                                                    |

| 3.7.2                 | Breakpoints                                                                                       |

| 3.7.3<br>3.7.4        | Debug Watchpoint (DCAPT)                                                                          |

| 3.7.5                 | Execution Control                                                                                 |

| 3.7.6                 | Parity Error Control                                                                              |

| 3.8<br>3.8.1          | Interrupts and Exceptions                                                                         |

| 3.8.2                 | INT_STAT0 Register         21           INT_STAT1 Register         21                             |

| 3.8.3                 | Thread Interrupt Mask 22                                                                          |

| 3.8.4                 | Multithreading Break                                                                              |

| 3.8.5<br>3.9          | Forcing an Interrupt                                                                              |

| 3.10                  | Crystal Oscillator                                                                                |

| 3.11                  | Clock Output Generator                                                                            |

| 3.12                  | Reset                                                                                             |

| <b>4.0 INS</b><br>4.1 | truction Set 26<br>Operand Addressing                                                             |

| 4.1                   | Addressing Modes                                                                                  |

| 4.2.1                 | The Register Address Space                                                                        |

| 4.3<br>4.3.1          | Instruction Set Summary                                                                           |

| 4.3.1                 | Shift and Bit-Field Operations                                                                    |

| 4.3.3                 | Single Bit Operations 34                                                                          |

| 4.3.4<br>4.3.5        | Data Movement And Extension Instructions                                                          |

| 4.3.6                 | Program Control Instructions                                                                      |

| 4.4                   | Instruction Formats and Encoding                                                                  |

| 5.0 Per               | ripherals 43                                                                                      |

| 5.1                   | Overview         43           SHARED PORT ARCHITECTURE         43                                 |

| 5.2<br>5.2.1          | SHARED PORT ARCHITECTURE                                                                          |

| 5.2.2                 | Interrupts                                                                                        |

| 5.2.3                 | FIFO Management       43         EXTERNAL FLASH CONTROLLER       45                               |

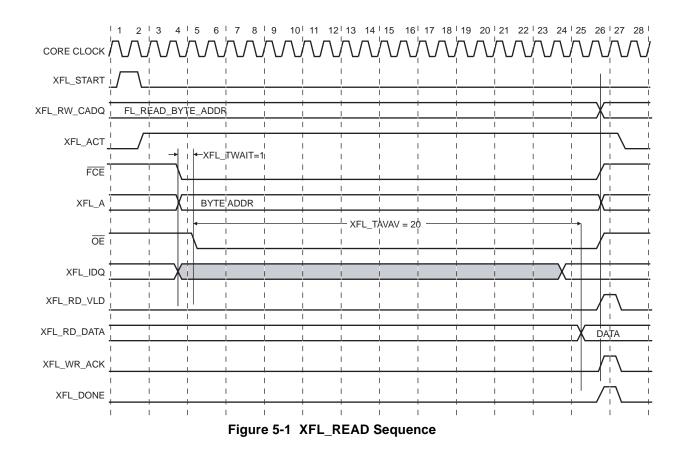

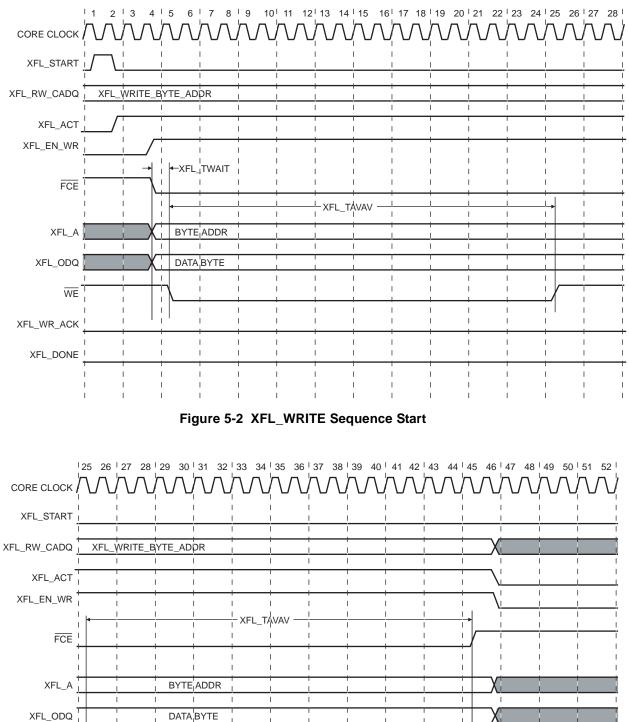

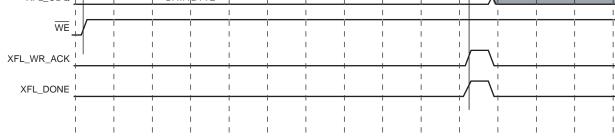

| 5.3                   | EXTERNAL FLASH CONTROLLER                                                                         |

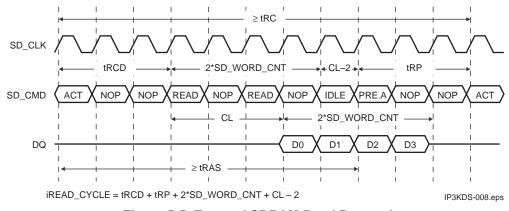

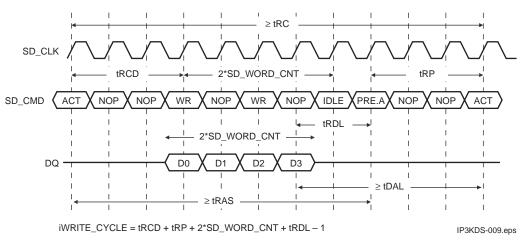

| 5.3.1<br>5.3.2        | Processor IREAD Interface                                                                         |

| 5.3.3                 | Configuring the Flash Controller                                                                  |

| 5.3.4                 | Using the Flash Controller                                                                        |

| 5.3.5<br>5.4          | Switching Between Flash and SDRAM                                                                 |

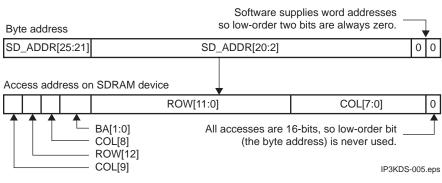

| 5.4.1                 | Address Translation                                                                               |

| 5.4.2                 | Configuring the SDRAM Controller                                                                  |

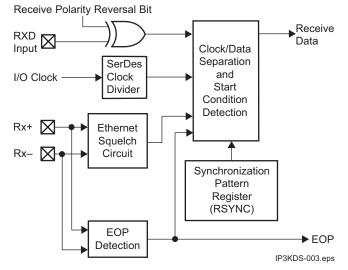

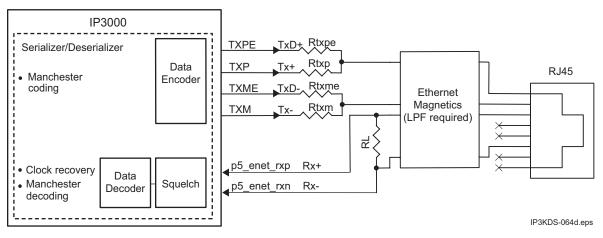

| 5.5<br>5.5.1          | SERIALIZER/DESERIALIZER (SerDes)                                                                  |

| 5.5.2                 | SerDes Configuration                                                                              |

|                       |                                                                                                   |

| IP3023 | Data | Sheet |

|--------|------|-------|

|--------|------|-------|

| 5.5.3            | Protocol Modes                              | 64         |

|------------------|---------------------------------------------|------------|

| 5.5.4            | 10base-T Ethernet                           |            |

| 5.5.5            | USB                                         | 69         |

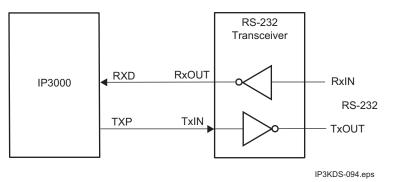

| 5.5.6            | UART                                        | 71         |

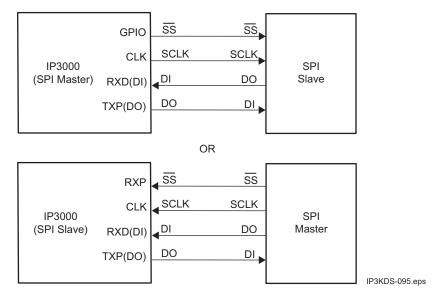

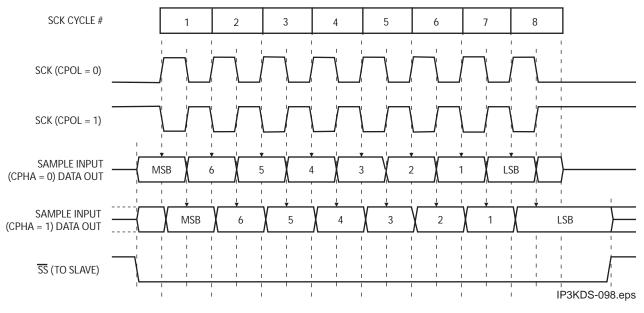

| 5.5.7            | SPI                                         | 72         |

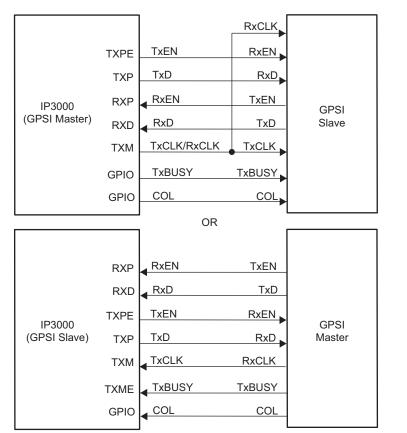

| 5.5.8            | SerDes-Based GPSI                           | 15         |

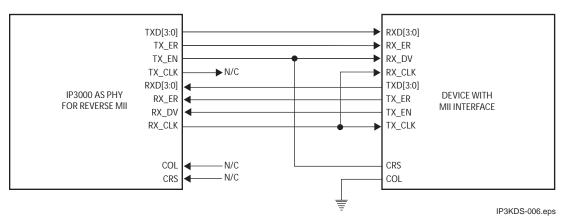

| 5.6<br>5.6.1     | MEDIA INDEPENDENT INTERFACE (MII)           | 11         |

| 5.6.2            | Receive Sequence                            | 70         |

| 5.6.3            | Physical-Side Mode                          | 80         |

| 5.7              | GENERAL PURPOSE SERIAL INTERFACE (GPSI)     | 81         |

| 5.7.1            | Interface Signal Description                | 81         |

| 5.7.2            | Receive Sequence                            | 82         |

| 5.7.3            | Transmit Sequence                           | 83         |

| 5.7.4            | Master Mode                                 | 84         |

| 5.8              | EXTERNAL INTERRUPTS                         | 85         |

| 5.9<br>5.9.1     | Timers, Clocks, and Random Number Generator | 80         |

| 5.9.1            | Multipurpose TimerSystem Timer              | 20         |

| 5.9.2            | Random Number Generator.                    |            |

| 5.10             | Debug Interface                             | 86         |

|                  | -                                           |            |

|                  | mory Reference                              | 88         |

| 6.1              | Alphabetical List of Registers              | 01         |

| 6.2<br>6.2.1     | Per-Thread Registers                        | 91         |

| 6.2.2            | ROSR                                        | 92         |

| 6.2.3            | INT_MASK0                                   |            |

| 6.2.4            | INT_MASK1                                   | 93         |

| 6.3              | Global Registers                            | <u>9</u> 3 |

| 6.3.1            | CHIP_ID                                     | 96         |

| 6.3.2            | INT_STAT0                                   |            |

| 6.3.3            | INT_STAT1                                   |            |

| 6.3.4            | GLOBAL_CTRL                                 |            |

| 6.3.5<br>6.3.6   | DCAPT (Data Capture Address)DCAPT_TNUM      | 97         |

| 6.4              | HRT Tables                                  | 90         |

| 6.5              | Timers, Clocks, and RNG Registers           | gq         |

| 6.6              | Per-Port Registers                          | 102        |

| 6.6.1            | Port Function Select Register.              | 104        |

| 6.6.2            | Port Interrupt Registers                    | 104        |

| 6.6.3            | Port Function Status 1                      | 105        |

| 6.7              |                                             | 105        |

| 6.7.1            |                                             | 105        |

| 6.7.2<br>6.7.3   |                                             | 106<br>107 |

| 6.8              |                                             | 107        |

| 6.8.1            |                                             | 107        |

| 6.8.2            |                                             | 108        |

| 6.9              |                                             | 109        |

| 6.9.1            |                                             | 109        |

| 6.9.2            |                                             | 110        |

| 6.10             |                                             | 112<br>112 |

| 6.10.1<br>6.10.2 |                                             | 113        |

| 6.11             |                                             | 115        |

| 6.11.1           |                                             | 115        |

| 6.11.2           |                                             | 116        |

| 6.11.3           | Port E MII Function                         | 118        |

| 6.11.4           | Port E High-Speed GPSI Function             | 120        |

| 6.12             |                                             | 121        |

| 6.12.1           |                                             | 121        |

| 6.12.2<br>6.12.3 |                                             | 122<br>124 |

| 6.12.5           |                                             | 124        |

| 6.13.1           |                                             | 124        |

| 6.14             |                                             | 124        |

| 6.14.1           |                                             | 124        |

| 6.14.2           | Port H MII Function                         | 125        |

| 6.14.3           | Port H Clock Function                       | 127        |

| 7.0 Ele          | ectrical Specifications                     | 128        |

| 7.1              |                                             | 128        |

| 7.2              |                                             | 129        |

| 7.3              | AC Specifications                           | 131        |

| 8.0 Pa           |                                             | 133        |

|                  | -                                           |            |

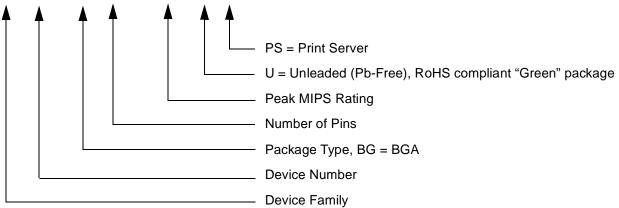

| 9.0 Pa           | rt Numbering                                | 134        |

|                  |                                             |            |

# 1.1 Additional Features

#### **IP3023 Wireless Network Processor Capabilities**

Foundation for Highly Flexible Connectivity Solution

- Performance: 250 MIPS @ 250MHz, 325MIPS @ 325MHz

- 250/325 MMACs performance from MAC unit with fixed point 16x16 multiply and 48-bit accumulator.

- On-chip dual-ported SRAM data memory.

- On-chip SRAM program memory.

- On-chip hardware for zero overhead instruction level context switch for multithreading.

- In-system programming of external flash.

# Multiple Networking Protocols and Physical Layer Support Hardware

- Two full-duplex serializer/deserializer (SerDes) channels.

- Flexible to support 10Base-T, GPSI, SPI, UART, USB protocols.

- One on-chip PHY function for 10Base-T Ethernet.

- Four MII Ports, each can operate in host or phy mode.

#### Memory

- 256 KB (64K x 33) on-chip program SRAM with 1-bit parity.

- 64 KB (16K x 32) on-chip dual port data SRAM.

- Up to 4 MB (4M x 8) off-chip flash support.

- Up to 64 MB (32M x 16) off-chip PC 66/100/133 SDRAM support.

#### **IP3023 Wireless Network Processor Features**

- 32-bit data and instruction paths (fixed instruction width).

- Instructions execute at the rate of one per clock cycle.

- Eight-way instruction level multithreading with support for both hard real time and non-real-time thread priority scheduling.

- Multiply and multiply/accumulate (MAC) instructions, where MAC uses a 48-bit accumulator.

- Special purpose CRC instruction for CRC generation/checking and encryption.

- Sixteen general-purpose 32-bit registers per thread (128 total).

- Eight 32-bit address registers per thread (64 total).

- High instruction code density.

#### **General-Purpose Hardware Peripherals**

- True random number generator (32-bit seed number).

- One 32-bit system timer synchronous with system clock with eight compare registers.

- One 32-bit real-time timer (one mode of the Multipurpose Timer) with constant clock frequency.

- Watchdog 32-bit timer with constant clock frequency.

- Power-on reset circuit.

- Eight external interrupt inputs mapped to I/O ports.

- Two programmable output clocks.

#### Sophisticated Power and Frequency/Clock Management Support

- Operating voltage from 1.14V to 1.26V.

- Single clock input with 10–20 MHz crystal clock input support.

- Two on-chip PLLs: one for processor clock, one for serial I/O.

- Core clock using a selectable on-chip divider.

- Software CPU speed control for power saving.

- Power-on reset (POR) logic.

- Auxiliary I/O clock input for serial I/O PLL.

#### Flexible I/O

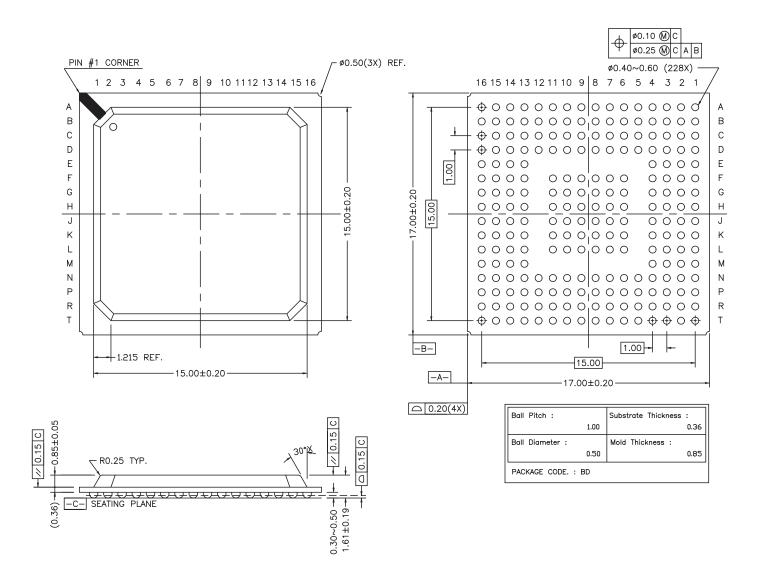

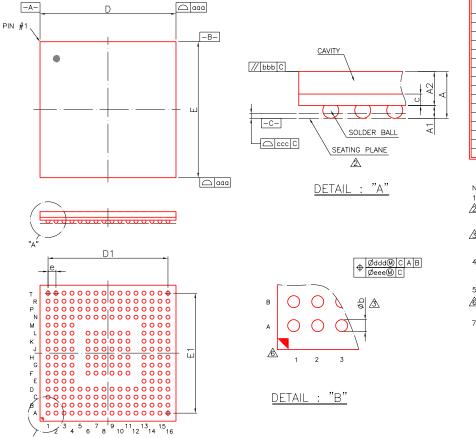

- 138 I/O pins in 228-pin 17x17mm BGA option.

- Eight configurable multifunction I/O ports.

- 3.3V symmetric CMOS output drive.

- 5V-tolerant I/O.

#### Support for In-System Debug and Configuration

- Customer application program updatable.

Run-time self programming.

- On-chip in-system debugging support interface.

- Debugging at full IP3023 operating speed.

#### **Complete Software Development Environment**

The IP3023 wireless network processor is capable of supporting the following functions in software. See a Ubicom sales representative for availability and schedule.

- ipOS<sup>™</sup> operating system

- ipModule<sup>™</sup> software pre-built connectivity modules complete software solutions and platform for wireless routers, access points, bridges, print servers, network cameras, and many other embedded network client applications. Includes core networking stack, numerous wired and wireless PHY layers and interfaces, plus application layer ipModules for WebServer, DNS, SMTP email, SNMP remote management, DHCP client/server, and NAT routing, to name a few.

- Red Hat<sup>®</sup> GNUPro<sup>®</sup> tools.

- Includes GCC ANSI C compiler and assembler, linker, utilities, and GNU debugger.

- Configuration tool.

- Integrated tool to support rapid development efforts.

- Ubicom's Unity<sup>™</sup> integrated development environment (IDE).

- Includes editor, project manager, graphical user interface to GNU debugger, device programmer, ipModule configuration tool, and profiler.

- Profiler for performance tuning.

#### 1.2 I/O Port Mapping

The IP3023 has highly configurable port mapping. Port A, for example, supports the external flash, but can also be shared with the SDRAM controller and a PCMCIA interface when combined with Port B. Some of the ports share a dedicated hardware function. Port E, for example, shares a part of an MII port, one of the on-board SerDes units, or part of a Utopia bus implementation in software. All ports (except Port A) can be used as GPIO ports, giving up to 106 GPIO pins. GPIO ports are used to create virtual I/O ports to control UTOPIA, 802.11a/b/g, PCM Highway, and other popular interfaces. Table 1-1 shows how the IP3023 I/O ports are shared and shows possible I/O port mappings for three different applications.

#### 1.3 Architecture

#### 1.3.1 CPU

The CPU is a general-purpose 32-bit pipelined processor. The CPU implements multithreading in hardware and supports the execution of deterministic hard real-time (HRT) threads. Up to eight simultaneous threads are supported in hardware. Code for the processing core is written in C as well as in assembly language.

#### 1.3.2 CPU Instruction Memory

The instruction memory for the main processor is implemented as a single-port (256 KB with parity, 64K x 32) SRAM. This RAM is able to supply the main processor with one instruction access per clock.

#### 1.3.3 CPU Data Memory

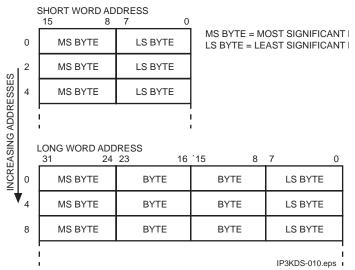

The data memory for the main processor is 64 KB (16K x 32) SRAM. It is able to perform one read and one write per clock, in support of the three-operand and memory-tomemory instruction set architecture.

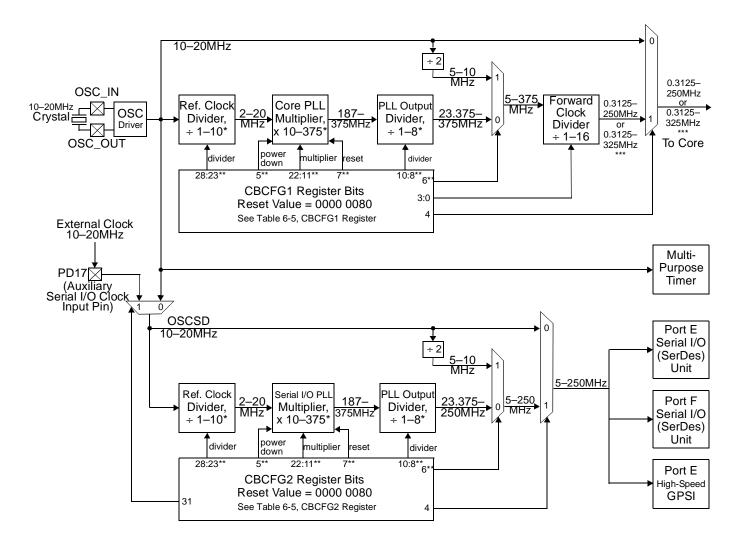

#### 1.3.4 Clocks, Frequency, and Timers

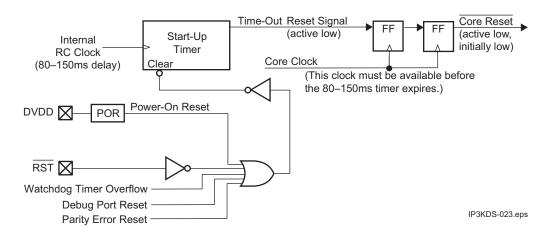

A single clock input (crystal, 10–20 MHz) is used to source multiple subsystems and peripherals in the IP3023. This clock source is fed into independent PLLs for generating a system clock and a serial I/O clock. Alternatively, the PLLs can be bypassed, and the 10–20 MHz clock input can be used directly. The PLLs are capable of generating up to a 250 MHz core clock from the 10–20 MHz input signal, or up to 325MHz on the 325MHz rated version.

This 10–20 MHz input is also fed into a real-time clock (RTC) timer portion of the multipurpose timer, which can be used to maintain an accurate time base in a system.

| I/O Port | Port Width<br>(bits) | Actual Hardware<br>I/O Support           | Dual / Multimode<br>Access Point | Print Server<br>Bridge | Networked Embedded<br>Devices |

|----------|----------------------|------------------------------------------|----------------------------------|------------------------|-------------------------------|

| Port A   | 32                   | Flash                                    | Flash                            | Flash                  | Flash                         |

| Port B   | 8                    | SDRAM                                    | GPIO / SDRAM (opt.)              | GPIO / SDRAM (opt.)    | GPIO / SDRAM (opt.)           |

| Port C   | 16                   | MII                                      | GPIO                             | GPIO                   | GPIO                          |

| Port D   | 18                   | MII                                      | MII                              | MII                    | MI                            |

| Port E   | 8                    | SerDes or MII (1/2)<br>or Hi-Speed GPSI. | GPOI                             | GPIO                   | GPIO                          |

| Port F   | 8                    | SerDes or MII (1/2)                      | GPIO                             | USB                    | GPIO                          |

| Port G   | 32                   | GPIO                                     | 802.11                           | 802.11                 | 802.11                        |

| Port H   | 16                   | MII                                      | (a and g)                        | (a or g)               | (a or g)                      |

# 1.3.5 Reduced Power Operation

The IP3023 can be configured for lower power operation by varying the frequency of operation and clock source. These lower power modes include:

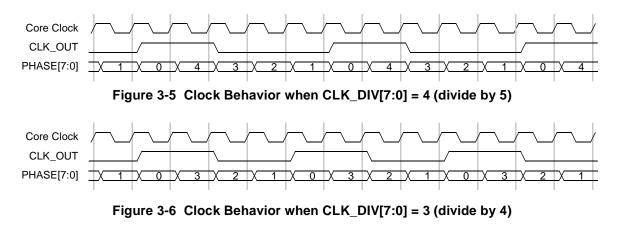

- Reducing the clock frequency from the system clock *PLL*. The clock circuit of the IP3023 includes a runtime controllable CPU clock, which allows the developer to reduce operating frequency (see Figure 3-3).

- *Turning off system clock PLL.* System clocking runs directly from the 10–20 MHz clock input.

#### 1.3.6 Interrupts

The IP3023 provides a flexible interrupt structure. Realtime interrupts are individually assigned to independent threads. An interrupt awakens the corresponding thread, if it was waiting, and the thread handles the interrupt with the priority and processor cycles assigned to the thread. If needed, the structure of a traditional interrupt service routine (ISR) can be emulated.

#### 1.3.7 Reset

The following sources are capable of causing a chip reset:

- Power-on

- Debug port

- Watchdog timer (one mode of the multipurpose timer)

- Parity error in on-chip instruction memory

- External reset (RST pin)

#### 1.3.8 Programming and Debugging

The IP3023 device has advanced in-system programming and debug support on-chip. This unobtrusive capability is provided through a Debug Interface. There is no need for a bond-out chip for software development. This eliminates concerns about differences in electrical characteristics between a bond-out chip and the actual chip used in the target application. Designers can test and revise code on the same part used in the actual application.

Ubicom provides the complete Red Hat GNUPro tools, including C compiler, assembler, linker, utilities, and GNU debugger. In addition, Ubicom offers an integrated graphical development environment which includes an editor, project manager, graphical user interface for the GNU debugger, device programmer, ipModule configuration tool, and profiler.

#### 1.3.9 Other Supported Functions

- Random-number generator. The IP3023 includes an on-chip hardware true random number generator. Onchip random noise generates random bits which are accumulated in a hardware 32-bit linear feedback shift register (LFSR). This function can be used to seed a software random number generator or to generate per-session cryptography keys.

- Boot from external flash. Unlike the IP2000 family processors, there is no on-chip flash. At start-up, the IP3023 is configured to execute instructions from its external flash port.

# 2.0 Pin Definitions

# 2.1 228-Pin BGA

|   | 1               | 2               | 3                | 4                | 5                | 6                | 7                | 8                | 9                | 10              | 11              | 12              | 13               | 14               | 15               | 16               |   |

|---|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|------------------|------------------|------------------|------------------|---|

| Α | РВ6<br><b>О</b> | РВ1<br><b>О</b> | PA27<br><b>O</b> | PA24<br>O        | PA21<br><b>O</b> | PA19<br><b>O</b> | PA16<br><b>O</b> | PA13<br><b>O</b> | PA12<br><b>O</b> | PA9<br><b>O</b> | PA6<br><b>O</b> | PA3<br><b>O</b> | PA1<br><b>O</b>  | PH14<br>O        | PH10<br><b>O</b> | РН5<br><b>О</b>  | A |

| в | РВ7<br><b>О</b> | РВ2<br><b>О</b> | PA30<br><b>O</b> | PA26<br><b>O</b> | PA23<br><b>O</b> | PA20<br><b>O</b> | PA17<br><b>O</b> | PA14<br><b>O</b> | PA11<br><b>O</b> | PA8<br><b>O</b> | PA5<br>O        | PA2<br>O        | PH15<br><b>O</b> | PH12<br><b>O</b> | PH7<br>O         | PH2<br>O         | в |

| С | PE2<br>O        | РВ3<br><b>О</b> | PA31<br><b>O</b> | PA28<br><b>O</b> | PA25<br>O        | PA22<br><b>O</b> | PA18<br><b>O</b> | PA15<br><b>O</b> | PA10<br><b>O</b> | PA7<br>O        | PA4<br>O        | PA0<br>O        | PH13<br><b>O</b> | PH9<br>O         | PH6<br>O         | PH0<br>O         | c |

| D | PE4<br>O        | РВ5<br><b>О</b> | РВ0<br><b>О</b>  | PA29<br><b>O</b> | IOVDD<br>O       | DVDD<br>O        |                  | DVDD<br>O        | DVDD<br>O        |                 | DVDD<br>O       | DVDD<br>O       | РН11<br><b>О</b> | PH8<br>O         | PH4<br>O         | PG29<br><b>O</b> | D |

| Е | PE5<br><b>O</b> | PE0<br>O        | РВ4<br><b>О</b>  | dvdd<br>O        |                  |                  |                  | IP3              | 023              |                 |                 |                 |                  | РН3<br><b>О</b>  | PH1<br>O         | PG28<br>O        | E |

| F | PF0<br>O        | PE3<br><b>O</b> | PE1<br>O         | dvdd<br>O        |                  | IOVSS<br>O       | IOVSS<br>O       | DVSS<br>O        | DVSS<br>O        | IOVSS<br>O      | DVDD<br>O       |                 |                  | PG31<br><b>O</b> | PG30<br><b>O</b> | PG25<br>O        | F |

| G | PF1<br>O        | PE7<br>O        | PE6<br><b>O</b>  | IOVDD<br>O       |                  | IOVSS<br>O       | IOVSS<br>O       | DVSS<br>O        | DVSS<br>O        | IOVSS<br>O      | IOVSS<br>O      |                 | DVDD<br>O        | PG27<br>O        | PG26<br>O        | PG24<br>O        | G |

| н | PF5<br>O        | PF3<br>O        | PF2<br>O         | IOVDD<br>O       |                  | DVSS<br>O        | DVSS<br>O        | DVSS<br>O        | DVSS<br>O        | DVSS<br>O       | DVSS<br>O       |                 |                  | PG23<br><b>O</b> | PG22<br><b>O</b> | PG21<br><b>O</b> | н |

| J | PF7<br>O        | PF6<br>O        | PF4<br>O         |                  |                  | IOVSS<br>O       | DVSS<br>O        | DVSS<br>O        | DVSS<br>O        | DVSS<br>O       | IOVSS<br>O      |                 |                  | PG18<br><b>O</b> | PG19<br><b>O</b> | PG20<br>O        | J |

| к | TEST2           | PLL2VSS<br>O    | PLL1VSS<br>O     | IOVDD<br>O       |                  | IOVSS<br>O       | IOVSS<br>O       | DVSS<br>O        | DVSS<br>O        | IOVSS<br>O      | IOVSS<br>O      |                 | DVDD<br>O        | PG14<br><b>O</b> | PG15<br><b>O</b> | PG17<br><b>O</b> | ĸ |

| L | PLL2VDD<br>O    | IOVSS<br>O      |                  | IOVDD<br>O       |                  | DVDD<br>O        | IOVSS<br>O       | DVSS<br>O        | DVSS<br>O        | IOVSS<br>O      | IOVSS<br>O      |                 |                  | PG10<br><b>O</b> | PG12<br><b>O</b> | PG16<br><b>O</b> | L |

| М | PLL1VDD<br>O    | A1VDD<br>O      | PFRDN<br>O       | dvdd<br>O        |                  | Тор              | View             | Thre             | ough             | Pac             | kage            | 9               |                  | PG5<br>O         | PG8<br>O         | PG13<br><b>O</b> | м |

| N | osc_in<br>O     | A1VSS<br>O      | PFRDP<br>O       | tsck<br>O        |                  |                  | DVDD<br>O        | DVDD<br>O        | dvdd<br>O        |                 | DVDD<br>O       | DVDD<br>O       | PG0<br>O         | PG3<br>O         | PG6<br>O         | PG11<br><b>O</b> | N |

| Р | OSC_OUT         | A2VSS<br>O      | TSS<br>O         | tso<br>O         | PD1<br>O         | PD5<br>O         | PD8<br>O         | PD12<br><b>O</b> | PD16<br><b>O</b> | PC2<br><b>O</b> | PC6<br><b>O</b> | PC9<br><b>O</b> | PC12<br><b>O</b> | PG1<br>O         | PG4<br>O         | PG9<br>O         | P |

| R | A2VDD<br>O      | TESTO<br>O      | TSI<br>O         | PD0<br>O         | PD3<br><b>O</b>  | PD6<br>O         | PD9<br>O         | PD13<br><b>O</b> | PD15<br>O        | PC1<br><b>O</b> | PC4<br>O        | PC7<br><b>O</b> | PC10<br><b>O</b> | PC13<br><b>O</b> | PC15<br><b>O</b> | PG7<br>O         | R |

| т | TEST1<br>O      | RST<br>O        | PD17<br><b>O</b> | PD2<br>O         | PD4<br>O         | PD7<br>O         | PD10<br><b>O</b> | PD11<br><b>O</b> | PD14<br>O        | PC0<br><b>O</b> | PC3<br><b>O</b> | PC5<br><b>O</b> | PC8<br><b>O</b>  | PC11<br><b>O</b> | PC14<br><b>O</b> | PG2<br>O         | т |

|   | 1               | 2               | 3                | 4                | 5                | 6                | 7                | 8                | 9                | 10              | 11              | 12              | 13               | 14               | 15               | 16               |   |

|   |                 |                 |                  |                  | Figure           | e 2-1 I          | P3023            | BGA              | Pin D            | efinitio        | on (To          | p View          | /)               |                  |                  |                  |   |

Figure 2-1 IP3023 BGA Pin Definition (Top View)

Table 2-1 Pin Assignments (sorted by pin number)

| Pin      | Signal       | Pin      | Signal         | Pin      | Signal        | Pin | Signal     |

|----------|--------------|----------|----------------|----------|---------------|-----|------------|

| A1       | PB6          | D10      | IOVDD          | J1       | PF7           | N8  | DVDD       |

| A2       | PB1          | D11      | DVDD           | J2       | PF6           | N9  | DVDD       |

| A3       | PA27         | D12      | DVDD           | J3       | PF4           | N10 | IOVDD      |

| A4       | PA24         | D13      | PH11           | J4       | DVDD          | N11 | DVDD       |

| A5       | PA21         | D14      | PH8            | J6       | IOVSS         | N12 | DVDD       |

| A6       | PA19         | D15      | PH4            | J7       | DVSS          | N13 | PG0        |

| A7       | PA16         | D16      | PG29           | J8       | DVSS          | N14 | PG3        |

| A8       | PA13         | E1       | PE5            | J9       | DVSS          | N15 | PG6        |

| A9       | PA12         | E2       | PE0            | J10      | DVSS          | N16 | PG11       |

| A10      | PA9          | E3       | PB4            | J11      | IOVSS         | P1  | OSC_OUT    |

| A11      | PA6          | E4       | DVDD           | J13      | IOVDD         | P2  | A2VSS      |

| A12      | PA3          | E13      | IOVDD          | J14      | PG18          | P3  | TSS        |

| A13      | PA1          | E14      | PH3            | J15      | PG19          | P4  | TSO        |

| A14      | PH14         | E15      | PH1            | J16      | PG20          | P5  | PD1        |

| A15      | PH10         | E16      | PG28           | K1       | TEST2         | P6  | PD5        |

| A16      | PH5          | F1       | PF0            | K2       | PLL2VSS       | P7  | PD8        |

| B1       | PB7          | F2       | PE3            | K3       | PLL1VSS       | P8  | PD12       |

| B2       | PB2          | F3       | PE1            | K4       | IOVDD         | P9  | PD16       |

| B3       | PA30         | F4       | DVDD           | K6       | IOVSS         | P10 | PC2        |

| В3<br>В4 |              | F4       |                | K0<br>K7 |               | P10 |            |

| -        | PA26<br>PA23 | F0<br>F7 | IOVSS<br>IOVSS | K8       | IOVSS<br>DVSS | P12 | PC6<br>PC9 |

| B5       |              |          |                |          |               |     |            |

| B6       | PA20         | F8       | DVSS           | K9       | DVSS          | P13 | PC12       |

| B7       | PA17         | F9       | DVSS           | K10      | IOVSS         | P14 | PG1        |

| B8       | PA14         | F10      | IOVSS          | K11      | IOVSS         | P15 | PG4        |

| B9       | PA11         | F11      | DVDD           | K13      | DVDD          | P16 | PG9        |

| B10      | PA8          | F13      | IOVDD          | K14      | PG14          | R1  | A2VDD      |

| B11      | PA5          | F14      | PG31           | K15      | PG15          | R2  | TEST0      |

| B12      | PA2          | F15      | PG30           | K16      | PG17          | R3  | TSI        |

| B13      | PH15         | F16      | PG25           | L1       | PLL2VDD       | R4  | PD0        |

| B14      | PH12         | G1       | PF1            | L2       | IOVSS         | R5  | PD3        |

| B15      | PH7          | G2       | PE7            | L3       | IOVDD         | R6  | PD6        |

| B16      | PH2          | G3       | PE6            | L4       | IOVDD         | R7  | PD9        |

| C1       | PE2          | G4       | IOVDD          | L6       | DVDD          | R8  | PD13       |

| C2       | PB3          | G6       | IOVSS          | L7       | IOVSS         | R9  | PD15       |

| C3       | PA31         | G7       | IOVSS          | L8       | DVSS          | R10 | PC1        |

| C4       | PA28         | G8       | DVSS           | L9       | DVSS          | R11 | PC4        |

| C5       | PA25         | G9       | DVSS           | L10      | IOVSS         | R12 | PC7        |

| C6       | PA22         | G10      | IOVSS          | L11      | IOVSS         | R13 | PC10       |

| C7       | PA18         | G11      | IOVSS          | L13      | IOVDD         | R14 | PC13       |

| C8       | PA15         | G13      | DVDD           | L14      | PG10          | R15 | PC15       |

| C9       | PA10         | G14      | PG27           | L15      | PG12          | R16 | PG7        |

| C10      | PA7          | G15      | PG26           | L16      | PG16          | T1  | TEST1      |

| C11      | PA4          | G16      | PG24           | M1       | PLL1VDD       | T2  | RST        |

| C12      | PA0          | H1       | PF5            | M2       | A1VDD         | T3  | PD17       |

| C13      | PH13         | H2       | PF3            | M3       | PFRDN         | T4  | PD2        |

| C14      | PH9          | H3       | PF2            | M4       | DVDD          | T5  | PD4        |

| C15      | PH6          | H4       | IOVDD          | M13      | IOVDD         | T6  | PD7        |

| C16      | PH0          | H6       | DVSS           | M14      | PG5           | T7  | PD10       |

| D1       | PE4          | H7       | DVSS           | M15      | PG8           | T8  | PD11       |

| D2       | PB5          | H8       | DVSS           | M16      | PG13          | T9  | PD14       |

| D3       | PB0          | H9       | DVSS           | N1       | OSC_IN        | T10 | PC0        |

| D4       | PA29         | H10      | DVSS           | N2       | A1VSS         | T11 | PC3        |

| D5       | IOVDD        | H11      | DVSS           | N3       | PFRDP         | T12 | PC5        |

| D6       | DVDD         | H13      | IOVDD          | N4       | TSCK          | T13 | PC8        |

| D7       | IOVDD        | H14      | PG23           | N5       | IOVDD         | T14 | PC11       |

| D8       | DVDD         | H15      | PG22           | N6       | IOVDD         | T15 | PC14       |

| D9       | DVDD         | H16      | PG21           | N7       | DVDD          | T16 | PG2        |

|          |              |          |                | -        |               |     |            |

|        | -   |         |     |        |     | -       |     |

|--------|-----|---------|-----|--------|-----|---------|-----|

| Signal | Pin | Signal  | Pin | Signal | Pin | Signal  | Pin |

| A1VDD  | M2  | IOVSS   | F6  | PB6    | A1  | PG3     | N14 |

| A1VSS  | N2  | IOVSS   | F7  | PB7    | B1  | PG4     | P15 |

| A2VDD  | R1  | IOVSS   | F10 | PC0    | T10 | PG5     | M14 |

| A2VSS  | P2  | IOVSS   | G6  | PC1    | R10 | PG6     | N15 |

| DVDD   | D6  | IOVSS   | G7  | PC2    | P10 | PG7     | R16 |

| DVDD   | D8  | IOVSS   | G10 | PC3    | T11 | PG8     | M15 |

| DVDD   | D9  | IOVSS   | G11 | PC4    | R11 | PG9     | P16 |

| DVDD   | D11 | IOVSS   | J6  | PC5    | T12 | PG10    | L14 |

| DVDD   | D12 | IOVSS   | J11 | PC6    | P11 | PG11    | N16 |

| DVDD   | E4  | IOVSS   | K6  | PC7    | R12 | PG12    | L15 |

| DVDD   | F4  | IOVSS   | K7  | PC8    | T13 | PG13    | M16 |

| DVDD   | F11 | IOVSS   | K10 | PC9    | P12 | PG14    | K14 |

| DVDD   | G13 | IOVSS   | K10 | PC10   | R13 | PG15    | K15 |

| DVDD   | J4  | IOVSS   | L2  | PC11   | T14 | PG16    | L16 |

| DVDD   | K13 | IOVSS   | L7  | PC12   | P13 | PG17    | K16 |

|        |     |         |     | -      |     |         |     |

| DVDD   | L6  | IOVSS   | L10 | PC13   | R14 | PG18    | J14 |

| DVDD   | M4  | IOVSS   | L11 | PC14   | T15 | PG19    | J15 |

| DVDD   | N7  | OSC_IN  | N1  | PC15   | R15 | PG20    | J16 |

| DVDD   | N8  | OSC_OUT | P1  | PD0    | R4  | PG21    | H16 |

| DVDD   | N9  | PA0     | C12 | PD1    | P5  | PG22    | H15 |

| DVDD   | N11 | PA1     | A13 | PD2    | T4  | PG23    | H14 |

| DVDD   | N12 | PA2     | B12 | PD3    | R5  | PG24    | G16 |

| DVSS   | F8  | PA3     | A12 | PD4    | T5  | PG25    | F16 |

| DVSS   | F9  | PA4     | C11 | PD5    | P6  | PG26    | G15 |

| DVSS   | G8  | PA5     | B11 | PD6    | R6  | PG27    | G14 |

| DVSS   | G9  | PA6     | A11 | PD7    | T6  | PG28    | E16 |

| DVSS   | H6  | PA7     | C10 | PD8    | P7  | PG29    | D16 |

| DVSS   | H7  | PA8     | B10 | PD9    | R7  | PG30    | F15 |

| DVSS   | H8  | PA9     | A10 | PD10   | T7  | PG31    | F14 |

| DVSS   | H9  | PA10    | C9  | PD11   | Т8  | PH0     | C16 |

| DVSS   | H10 | PA11    | B9  | PD12   | P8  | PH1     | E15 |

| DVSS   | H11 | PA12    | A9  | PD13   | R8  | PH2     | B16 |

| DVSS   | J7  | PA13    | A8  | PD14   | Т9  | PH3     | E14 |

| DVSS   | J8  | PA14    | B8  | PD15   | R9  | PH4     | D15 |

| DVSS   | J9  | PA15    | C8  | PD16   | P9  | PH5     | A16 |

| DVSS   | J10 | PA16    | A7  | PD17   | T3  | PH6     | C15 |

| DVSS   | K8  | PA17    | B7  | PE0    | E2  | PH7     | B15 |

| DVSS   | K9  | PA18    | C7  | PE1    | F3  | PH8     | D14 |

| DVSS   | L8  | PA19    | A6  | PE2    | C1  | PH9     | C14 |

| DVSS   | L9  | PA20    | B6  | PE3    | F2  | PH10    | A15 |

| IOVDD  | D5  | PA21    | A5  | PE4    | D1  | PH11    | D13 |

|        |     |         |     |        |     |         | -   |

|        | D7  | PA22    | C6  | PE5    | E1  | PH12    | B14 |

| IOVDD  | D10 | PA23    | B5  | PE6    | G3  | PH13    | C13 |

| IOVDD  | E13 | PA24    | A4  | PE7    | G2  | PH14    | A14 |

| IOVDD  | F13 | PA25    | C5  | PF0    | F1  | PH15    | B13 |

| IOVDD  | G4  | PA26    | B4  | PF1    | G1  | PLL1VDD | M1  |

| IOVDD  | H4  | PA27    | A3  | PF2    | H3  | PLL1VSS | K3  |

| IOVDD  | H13 | PA28    | C4  | PF3    | H2  | PLL2VDD | L1  |

| IOVDD  | J13 | PA29    | D4  | PF4    | J3  | PLL2VSS | K2  |

| IOVDD  | K4  | PA30    | B3  | PF5    | H1  | RST     | T2  |

| IOVDD  | L3  | PA31    | C3  | PF6    | J2  | TEST0   | R2  |

| IOVDD  | L4  | PB0     | D3  | PF7    | J1  | TEST1   | T1  |

| IOVDD  | L13 | PB1     | A2  | PFRDN  | M3  | TEST2   | K1  |

| IOVDD  | M13 | PB2     | B2  | PFRDP  | N3  | TSCK    | N4  |

| IOVDD  | N5  | PB3     | C2  | PG0    | N13 | TSI     | R3  |

| IOVDD  | N6  | PB4     | E3  | PG1    | P14 | TSO     | P4  |

|        |     |         |     |        |     |         |     |

# Table 2-2 Pin Assignments (sorted by signal name)

# 2.2 Pin Descriptions

Type Codes: I = Digital Input, AI = Analog Input, O/DO = Digital Output, HiZ = High Impedance, P = Power, PU = On-Chip Pullup, PD = On-Chip Pulldown, ST = Schmitt Trigger, NS = Non-Slew Rate Limited

| Name        | Туре    | Sink<br>@ 3.3V<br>IOVDD | Source<br>@ 3.3V<br>IOVDD | Description                                                                                                                             |

|-------------|---------|-------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| A1VDD       | P 1.2V  |                         |                           | VDD for analog blocks: power-on circuit, crystal oscillator and rc-oscillator                                                           |

| A1VSS       | P 0V    |                         |                           | VSS for analog blocks: power-on circuit, crystal oscillator and rc-oscillator                                                           |

| A2VDD       | P 1.2V  |                         |                           | VDD for squelch block only                                                                                                              |

| A2VSS       | P 0V    |                         |                           | VSS for squelch block only                                                                                                              |

| DVDD        | P 1.2V  |                         |                           | VDD for digital core                                                                                                                    |

| DVSS        | P 0V    |                         |                           | VSS for digital core                                                                                                                    |

| IOVDD       | P 3.3V  |                         |                           | VDD for I/Os                                                                                                                            |

| IOVSS       | P 0V    |                         |                           | VSS for I/Os                                                                                                                            |

| OSC_IN      | AI      |                         |                           | Crystal clock input                                                                                                                     |

| OSC_OUT     | O/HiZ   |                         |                           | Crystal clock output                                                                                                                    |

| PFRDN       | AI      |                         |                           | Port F Ethernet RXN                                                                                                                     |

| PFRDP       | AI      |                         |                           | Port F Ethernet RXP                                                                                                                     |

| PLL1VDD     | P 1.2V  |                         |                           | VDD for core clock PLL                                                                                                                  |

| PLL1VSS     | P 1.2V  |                         |                           | VSS for core clock PLL                                                                                                                  |

| PLL2VDD     | P 1.2V  |                         |                           | VDD for serial I/O clock PLL                                                                                                            |

| PLL2VSS     | P 1.2V  |                         |                           | VSS for serial I/O clock PLL                                                                                                            |

| PA[31:0]    | I/O     | 6 mA                    | 8 mA                      | Port A. Refer to Table 2-4.                                                                                                             |

| PB[7,5,3:0] | I/O     | 6 mA                    | 8 mA                      | Port B. Refer to Table 2-5.                                                                                                             |

| PB6         | I/O, NS | 16 mA                   | 16 mA                     | Port B. Refer to Table 2-5. See Note 2 below.                                                                                           |

| PB4         | I/O     | 6 mA                    | 8 mA                      | SDRAM enable – A pullup must be connected to this pin<br>if an external SRAM is used; if not, a pulldown should be<br>used. See Note 2. |

| PC[15:0]    | I/O     | 6 mA                    | 8 mA                      | Port C. Refer to Table 2-6.                                                                                                             |

| PD17        | I/O, ST | 6 mA                    | 8 mA                      | Port D. Auxiliary I/O clock input, refer to Table 2-7.                                                                                  |

| PD[16:0]    | I/O     | 6 mA                    | 8 mA                      | Port D. Refer to Table 2-7.                                                                                                             |

| PE[7:0]     | I/O     | 6 mA                    | 8 mA                      | Port E. Refer to Table 2-8.                                                                                                             |

| PF7         | I/O     | 6 mA                    | 8 mA                      | Port F. Refer to Table 2-9.                                                                                                             |

| PF[6:5]     | I/O     | 16 mA                   | 24 mA                     | Port F. Refer to Table 2-9.                                                                                                             |

| PF[4:0]     | I/O     | 6 mA                    | 8 mA                      | Port F. Refer to Table 2-9.                                                                                                             |

| PG[31:0]    | I/O     | 6 mA                    | 8 mA                      | Port G. Refer to Table 2-10.                                                                                                            |

| PH[15:0]    | I/O     | 6 mA                    | 8 mA                      | Port H. Refer to Table 2-11.                                                                                                            |

| Table | 2-3 | Pin | Descr | riptions |

|-------|-----|-----|-------|----------|

|-------|-----|-----|-------|----------|

| Name                                                                                                                                                                                                                                                                                                                                                                                   | Туре                                                                  | Sink<br>@ 3.3V<br>IOVDD | Source<br>@ 3.3V<br>IOVDD                                                                                      | Description                                                                               |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| RST                                                                                                                                                                                                                                                                                                                                                                                    | I/ST/PU                                                               |                         |                                                                                                                | Assert to 0 for chip reset. See Note 1.                                                   |  |  |  |  |

| TEST0, TEST1,<br>TEST2                                                                                                                                                                                                                                                                                                                                                                 | I, PD                                                                 |                         |                                                                                                                | Test mode pins. Connect to Vss. See Note 1.                                               |  |  |  |  |

| TSCK                                                                                                                                                                                                                                                                                                                                                                                   | I/ST/PD                                                               |                         |                                                                                                                | Debug Interface Clock (used only for in-system program-<br>ming and debug).               |  |  |  |  |

| TSS                                                                                                                                                                                                                                                                                                                                                                                    | I/ST/PU                                                               |                         |                                                                                                                | Debug Interface Slave Select (used only for in-system programming and debug). See Note 1. |  |  |  |  |

| TSI                                                                                                                                                                                                                                                                                                                                                                                    | I/ST/PU                                                               |                         |                                                                                                                | Debug Interface Serial Data Input (used only for in-sys-<br>tem programming and debug).   |  |  |  |  |

| TSO                                                                                                                                                                                                                                                                                                                                                                                    | O/HiZ                                                                 | 6 mA                    | 8 mA Debug Interface Serial Data output (used only for in-system programming and debug; high Z unless TSS low) |                                                                                           |  |  |  |  |

| Note 1:                                                                                                                                                                                                                                                                                                                                                                                | Note 1: Ubicom recommends not relying on internal pullup or pulldown. |                         |                                                                                                                |                                                                                           |  |  |  |  |

| Note 2: If the PB4 pin is pulled high at power up, the PB6 pin will output at least 2 clocks (for external SDRAM) at the frequency of the OSC_IN pin until the reset holdoff time expires, and then PB6 will behave normally (tri-stated until programmed by software). If the PB4 pin is pulled low during power up, the PB6 pin will remain tri-stated until programmed by software. |                                                                       |                         |                                                                                                                |                                                                                           |  |  |  |  |

#### Table 2-3 Pin Descriptions

## 2.3 I/O Ports Signal Maps

The eight I/O ports are designated Port A, Port B, ..., Port H. Every port is capable of multiple functions. Programs select the function of a port by programming the port's function select register. Behavior of each I/O port's signals depends on the function selected for that port. Table 2-4 through Table 2-11 show the signal assignments for each function of each port. Refer also to Section 5.0 on page 43 for more detail and for explanations of terms.

|                              | <b>5</b> 1            |                       |                      |

|------------------------------|-----------------------|-----------------------|----------------------|

| Port Bit #<br>PA[ <i>n</i> ] | Function 0<br>(Flash) | Function 1<br>(SDRAM) | Function 3<br>(GPIO) |

| 12:0                         | ADDR [12:0]           | ADDR [12:0]           | GPIO                 |

| 13                           | ADDR [13]             | BA [0]                | GPIO                 |

| 14                           | ADDR [14]             | BA [1]                | GPIO                 |

| 15                           | ADDR [15]             | DQM                   | GPIO                 |

| 16                           | ADDR [16]             | DATA [0]              | GPIO                 |

| 17                           | ADDR [17]             | DATA [1]              | GPIO                 |

| 18                           | ADDR [18]             | DATA [2]              | GPIO                 |

| 19                           | ADDR [19]             | DATA [3]              | GPIO                 |

| 20                           | ADDR [20]             | DATA [4]              | GPIO                 |

| 21                           | ADDR [21]             | DATA [5]              | GPIO                 |

| 22                           | OE                    | DATA [6]              | GPIO                 |

| Function 0<br>(Flash) | Function 1<br>(SDRAM)                                                                             | Function 3<br>(GPIO)                                                                                                                          |

|-----------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| WE                    | DATA [7]                                                                                          | GPIO                                                                                                                                          |

| DATA [0]              | DATA [8]                                                                                          | GPIO                                                                                                                                          |

| DATA [1]              | DATA [9]                                                                                          | GPIO                                                                                                                                          |

| DATA [2]              | DATA [10]                                                                                         | GPIO                                                                                                                                          |

| DATA [3]              | DATA [11]                                                                                         | GPIO                                                                                                                                          |

| DATA [4]              | DATA [12]                                                                                         | GPIO                                                                                                                                          |

| DATA [5]              | DATA [13]                                                                                         | GPIO                                                                                                                                          |

| DATA [6]              | DATA [14]                                                                                         | GPIO                                                                                                                                          |

| DATA [7]              | DATA [15]                                                                                         | GPIO                                                                                                                                          |

|                       | (Flash)<br>WE<br>DATA [0]<br>DATA [1]<br>DATA [2]<br>DATA [3]<br>DATA [4]<br>DATA [5]<br>DATA [6] | (Flash)(SDRAM)WEDATA [7]DATA [0]DATA [8]DATA [1]DATA [9]DATA [2]DATA [10]DATA [3]DATA [11]DATA [4]DATA [12]DATA [5]DATA [13]DATA [6]DATA [14] |

#### Table 2-5 Port B Signal Map

| Port Bit #<br>PB[ <i>n</i> ]                                    | Function 0<br>(Flash) | Function 1<br>(SDRAM +<br>Flash + Clock) | Function 2<br>(GPIO) |

|-----------------------------------------------------------------|-----------------------|------------------------------------------|----------------------|

| 0                                                               | GPIO                  | WE                                       | GPIO                 |

| 1                                                               | GPIO                  | RAS                                      | GPIO                 |

| 2                                                               | GPIO                  | CAS                                      | GPIO                 |

| 3                                                               | GPIO                  | CS                                       | GPIO                 |

| 4                                                               | GPIO                  | CKE                                      | GPIO                 |

| 5                                                               | GPIO                  | SD_CLK_IN                                | GPIO                 |

| 6                                                               | GPIO                  | CLK_OUT                                  | GPIO                 |

| 7                                                               | FCE*                  | FCE*                                     | GPIO                 |

| * A pullup should be placed on the $\overline{FCE}$ (Flash Chip |                       |                                          |                      |

\* A pullup should be placed on the FCE (Flash Chip Enable) pin so that the Flash isn't enabled while the IP3023 is in reset (while the IP3023 is floating the FCE pin).

#### Table 2-6 Port C Signal Map

| Port Bit #<br>PC[n] | Func 0<br>(GPIO) | Func 1<br>(MII) |

|---------------------|------------------|-----------------|

| 0                   | GPIO             | CRS             |

| 1                   | GPIO             | COL             |

| 2                   | GPIO             | TXD [3]         |

| 3                   | GPIO             | TXD [2]         |

| 4                   | GPIO             | TXD [1]         |

| 5                   | GPIO             | TXD [0]         |

| 6                   | GPIO             | TX_EN           |

| 7                   | GPIO             | TX_CLK          |

| 8                   | GPIO             | TX_ER           |

| 9                   | GPIO             | RX_ER           |

| 10                  | GPIO             | RX_CLK          |

| 11                  | GPIO             | RX_DV           |

| 12                  | GPIO             | RXD [0]         |

| 13                  | GPIO             | RXD [1]         |

| 14                  | GPIO             | RXD [2]         |

| 15                  | GPIO             | RXD [3]         |

Table 2-7 Port D Signal Map

| Port Bit #<br>PD[ <i>n</i> ]                           | Function 0 (GPIO) | Function 1 (MII) |

|--------------------------------------------------------|-------------------|------------------|

| 0                                                      | GPIO              | CRS              |

| 1                                                      | GPIO              | COL              |

| 2                                                      | GPIO              | TXD [3]          |

| 3                                                      | GPIO              | TXD [2]          |

| 4                                                      | GPIO              | TXD [1]          |

| 5                                                      | GPIO              | TXD [0]          |

| 6                                                      | GPIO              | TX_EN            |

| 7                                                      | GPIO              | TX_CLK           |

| 8                                                      | GPIO              | TX_ER            |

| 9                                                      | GPIO              | RX_ER            |

| 10                                                     | GPIO              | RX_CLK           |

| 11                                                     | GPIO              | RX_DV            |

| 12                                                     | GPIO              | RXD [0]          |

| 13                                                     | GPIO              | RXD [1]          |

| 14                                                     | GPIO              | RXD [2]          |

| 15                                                     | GPIO              | RXD [3]          |

| 16                                                     | GPIO              | GPIO             |

| 17*                                                    | GPIO              | GPIO             |

| <ul> <li>* Auxiliary serial I/O clock input</li> </ul> |                   |                  |

#### Table 2-8 Port E Signal Map

| Port Bit<br># PE[ <i>n</i> ] | Func 0<br>(GPIO) | Func 1<br>(SerDes) | Func 2<br>(1/2 MII) | Func 3<br>GPSI |

|------------------------------|------------------|--------------------|---------------------|----------------|

| 0                            | GPIO             | RXD                | CRS                 | RxD            |

| 1                            | GPIO             | RXM                | COL                 | COL            |

| 2                            | GPIO             | RXP                | TXD [3]             | RxEN           |

| 3                            | GPIO             | CLK                | TXD [2]             | RxCLK          |

| 4                            | GPIO             | TXME               | TXD [1]             | CRS/<br>TxBUSY |

| 5                            | GPIO             | ТХМ                | TXD [0]             | TxCLK          |

| 6                            | GPIO             | TXP                | TX_EN               | TxD            |

| 7                            | GPIO             | TXPE               | TX_CLK              | TxEN           |

| Port Bit #<br>PF[ <i>n</i> ] | Func 0<br>(GPIO) | Func 1<br>(SerDes) | Func 2<br>(1/2 MII) |

|------------------------------|------------------|--------------------|---------------------|

| 0                            | GPIO             | RXD                | TX_ER               |

| 1                            | GPIO             | RXM                | RX_ER               |

| 2                            | GPIO             | RXP                | RX_CLK              |

| 3                            | GPIO             | CLK                | RX_DV               |

| 4                            | GPIO             | TXME               | RXD [0]             |

| 5                            | GPIO             | ТХМ                | RXD [1]             |

| 6                            | GPIO             | ТХР                | RXD [2]             |

| 7                            | GPIO             | TXPE               | RXD [3]             |

#### Table 2-9 Port F Signal Map

#### Table 2-10 Port G Signal Map

| Port Bit # PG[n] | Function 0<br>(GPIO) |

|------------------|----------------------|

| 31:0             | GPIO                 |

#### Table 2-11 Port H Signal Map

| Pin<br>PH[ <i>n</i> ] | Func 0<br>(GPIO) | Func 1<br>(MII) | Func 2<br>(CLK) |

|-----------------------|------------------|-----------------|-----------------|

| 0                     | GPIO             | CRS             | GPIO            |

| 1                     | GPIO             | COL             | GPIO            |

| 2                     | GPIO             | TXD [3]         | GPIO            |

| 3                     | GPIO             | TXD [2]         | GPIO            |

| 4                     | GPIO             | TXD [1]         | GPIO            |

| 5                     | GPIO             | TXD [0]         | GPIO            |

| 6                     | GPIO             | TX_EN           | GPIO            |

| 7                     | GPIO             | TX_CLK          | GPIO            |

| 8                     | GPIO             | TX_ER           | GPIO            |

| 9                     | GPIO             | RX_ER           | GPIO            |

| 10                    | GPIO             | RX_CLK          | GPIO            |

| 11                    | GPIO             | RX_DV           | GPIO            |

| 12                    | GPIO             | RXD [0]         | GPIO            |

| 13                    | GPIO             | RXD [1]         | CLK_OUT         |

| 14                    | GPIO             | RXD [2]         | GPIO            |

| 15                    | GPIO             | RXD [3]         | GPIO            |

# 3.0 System Architecture

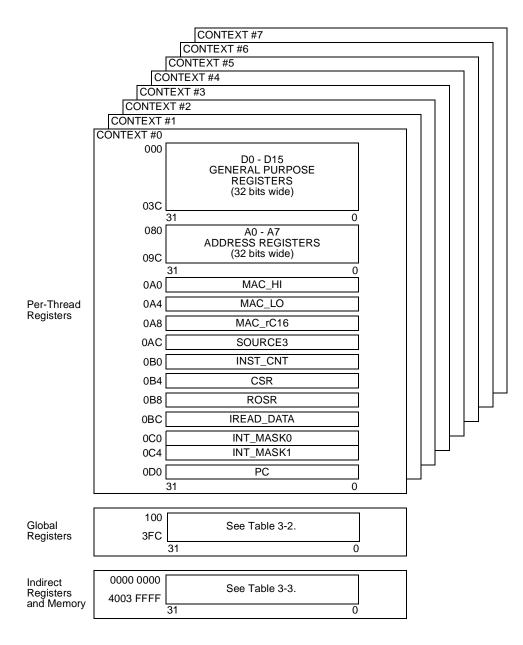

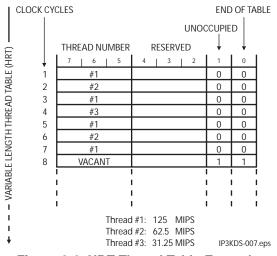

The central feature of the IP3023 architecture is hardware multithreading, with zero-overhead context switching between hardware threads. All registers that contain context-specific information are duplicated for each of eight hardware threads. The CPU hardware is capable of switching from one hardware thread to another, on a cycle-by-cycle basis with no switching delay. This design enables deterministic and extremely efficient interrupt response, which in turn supports the creation of *software peripherals*. A *software peripheral* is a combination of simple peripheral I/O hardware, and control logic implemented in software, rather than custom peripheral hardware.

#### 3.1 CPU Registers

The IP3023 features 16 general-purpose 32-bit data registers, eight 32-bit address registers (A0-A6, A7/SP), multiply/multiply-accumulate (MAC) output registers, and various other registers. These registers reside in the register address space, an address space separate from both the instruction and data memories. Instructions reference the registers within the register address space directly (as opposed to indirectly through offsets from an address base register). There is no capability for indirect referencing of registers in the register address space.

Every register in the register address space is 32 bits wide.

There are two distinct groups of registers in the register address space:

- Per-Thread Registers

- Global Registers

Some registers are described as read-only. Do not write to a read-only register. Writes to these registers do not change the state of the register, but may cause undesirable side effects.

Some registers are described as write-only. Reads of these registers return undefined results.

# 3.1.1 Per-Thread Registers

Per-thread registers define the architectural state of one hardware thread. The first 64 registers are per-thread; that is, to support immediate context switching (without the overhead of saving and restoring these registers in software), the per-thread register set is duplicated for each of the eight hardware-supported threads, as shown in Figure 3-1. Table 3-1 shows the locations of these registers in the register space. Refer also to Section 6.2 for detailed register descriptions.

Table 3-1 Per-Thread Register Map

| Address | Register(s) | Description                                                  |

|---------|-------------|--------------------------------------------------------------|

| 000-03C | D0–D15      | General-purpose data reg-<br>isters.                         |

| 040-07C | Reserved    |                                                              |

| 080-098 | A0–A6       | 32-bit address registers.                                    |

| 09C     | A7 or SP    | 32-bit stack pointer, also referred to as A7.                |

| 0A0     | MAC_HI      | Multiply-accumulate result, high 32-bits.                    |